|

Добрый день!

Скажите, пожалуйста,планируется ли продолжение курсов по нанотехнологиям? Спасибо, Евгений

|

Специфика построения аппаратных платформ высокопроизводительных вычислительных систем с микропрограммным уровнем доступа

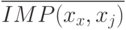

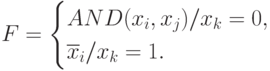

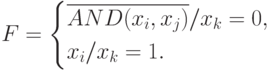

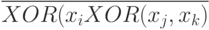

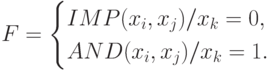

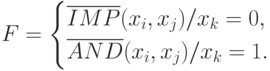

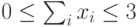

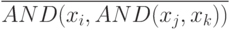

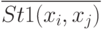

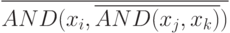

Взяв из каждого класса смежности по одному "типичному (и наглядному) представителю" (всего 14) и его инверсию, получим систему логических операций (первые 28 функций

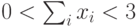

табл. 3.13), которая с помощью группы переименований переменных (порядка  !) покрывает весь класс ЛФ трех переменных (всего 256 функций). Дополнив выбранную таким образом систему команд (П)ПЗУ-бит-процессора конечно-автоматными функциями "арифметическая сумма" и "запоминание единицей", получим систему бит-инструкций

табл. 3.13, которая полностью совместима с Н1841 ВФ1.

!) покрывает весь класс ЛФ трех переменных (всего 256 функций). Дополнив выбранную таким образом систему команд (П)ПЗУ-бит-процессора конечно-автоматными функциями "арифметическая сумма" и "запоминание единицей", получим систему бит-инструкций

табл. 3.13, которая полностью совместима с Н1841 ВФ1.

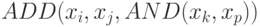

Существенно, что (П)ПЗУ-бит-процессор обеспечивает работу блоков, устройств и всего (П)ПЗУ-субпроцессора как в чисто конвейерном (бит-инструкции 31, 32

табл. 3.13), так и в векторно-конвейерном (бит-инструкции 29, 30

табл. 3.13) режимах, причем последний повышает темп обработки данных в  раз, где

раз, где  - разрядность арифметики субпроцессора.

- разрядность арифметики субпроцессора.

При расчете аппаратных затрат на (П)ПЗУ-бит-процессор (табл. 3.14) учитывалась "независимость" средств и объекта управления в каналах АЛУ и транзита, где "регистр команды" и средства коммутации реализуются через одни и те же контактные окна, на которые расходуется только площадь кристалла СБИС.

Представленная в табл. 3.13 система инструкций бит-процессора не покрывает всего многообразия реализуемых в операционном канале ЛФ и особенно конечно-автоматных функций, но, тем не менее, мощность множества доступных проблемно-ориентированному пользователю операций (всего 256+11 = 367) более чем на порядок выше, чем у репро-граммируемых бит-процессоров 2-й версии (всего 22 - см. табл. 3.9).

Поэтому удельные аппаратные затраты на одну доступную проблемно-ориентированному пользователю арифметико-логическую функцию в операционном канале (П)ПЗУ-бит-процессора (0,32 транзистора на функцию) более чем в 37 раз ниже, чем у репрограммируемых бит-процессоров 2-й версии (11,8 транзистора на функцию - см. табл. 3.9).

Если исходить из того, что дополнительные каналы гальванического транзита используются только под переименование входов-выходов, то коммутационные возможности (П)ПЗУ-бит-процессора можно оценить соотношениями (3.2) и (3.3) только при  (за счет появления диагональной связи).

(за счет появления диагональной связи).

| № | Преобразование | № | Преобразование | |

|---|---|---|---|---|

| 1 |  |

20 |  |

|

| 2 |  |

21 |  |

|

| 3 |  |

22 |  |

|

| 4 |  |

23 |  |

|

| 5 |  |

24 |  |

|

| 6 |  |

25 |  |

|

| 7 |  |

26 |  |

|

| 8 |  |

27 |  |

|

| 9 |  |

28 |  |

|

| 10 |  |

29 |  |

|

| 11 |  |

30 | \overline{ADD(x_i,x_j, AND(x_k,x_p))} | |

| 12 |  |

31 |  |

|

| 13 |  |

32 |  |

|

| 14 |  |

33 |  |

|

| 15 |  |

34 |  |

|

| 16 |  |

35 |  |

|

| 17 |  |

36 |  |

|

| 18 |  |

37 |  |

|

| 19 |  |

38 | СО(генерация константы) |

| Наименование блока | "Окон" | Транзисторов |

|---|---|---|

| Регистр инструкции (КОП) | 34 | - |

| Регистр инструкции (коммутация) | 98 | - |

| Операционные D-триггеры | - | 66 |

| АЛУ | - | 50 |

| Коммутационные D-триггеры | - | 44 |

| Итого на канал АЛУ | 34 | 116 |

| Итого на коммутацию | 98 | 44 |

| Итого на бит-процессор | 132 | 160 |

Поэтому коммутационные возможности:

- канала АЛУ при реализации асимметричных по всем трем операндам функций (25 и 26 функции

табл. 3.13):

![\mu_{1}= [(A^{3}_{5} ( C ^{1}_3 + 1) + C^{2}_{5} )] * A^{2}_5 = 1250](/sites/default/files/tex_cache/eed558042cadd2c0b80ab2d89f7184b4.png) коммутационных структур;

коммутационных структур; - канала транзита:

![\mu_{2}= [(A^{2}_{5} + A_{5}^1)(C^{2}_{3} + 1) + C^{2}_{5} )] * A_{5} = 610](/sites/default/files/tex_cache/82ad317f4a1b6aa3391bcd8e8e856d85.png) коммутационных структур;

коммутационных структур; - всего (П)ПЗУ-бит-процессора:

.

.

Из этих данных следует, что разнообразие реализуемых бит-процессором коммутационных структур возросло всего в 6 раз по отношению к репрограммируемым бит-процессорам 2-й версии (0,96*217 - см. табл. 3.12), но удельные аппаратные затраты (5,9*10-5 транзисторов на функцию) упали почти в 60 раз (34*10-4 транзисторов на функцию - см. табл. 3.12). При этом на управление и коммутацию расходуется только площадь кристалла, занимаемая либо перепрограммируемыми перемычками, либо контактными окнами, что обусловлено технологией (П)ПЗУ.

Таким образом, проведенный по критерию максимума функциональной интеграции синтез МКМД-бит-потоковых матриц показал:

- В классе булевых функций функциональную интенсивность использования одного такта бит-процессора можно повысить только за счет увеличения количества входных и выходных операндов АЛУ, для чего необходимо расширить структурно-функциональные возможности внутренних и внешних связей бит-процессора.

- Ассоциативное управление коммутационными и операционными ресурсами бит-процессора более эффективно при двухступенчатой системе управления АЛУ, которое в классе ЛФ

переменных представляет собой многофункциональный модуль с раздельными информационными и управляющими входами, а в классах ЛФ

переменных представляет собой многофункциональный модуль с раздельными информационными и управляющими входами, а в классах ЛФ  переменных - со смешанными информационными и управляющими входами.

переменных - со смешанными информационными и управляющими входами. - При двухступенчатом ассоциативном управлении локальные ассоциативные взаимодействия коммутационным и операционным ресурсами бит-процессора порождают глобальные ассоциативные взаимодействия на бит-матрице, что наиболее характерно для операторов фиксации переменных, используемых для функциональной подстройки АЛУ.