|

Добрый день!

Скажите, пожалуйста,планируется ли продолжение курсов по нанотехнологиям? Спасибо, Евгений

|

Специфика построения аппаратных платформ высокопроизводительных вычислительных систем с микропрограммным уровнем доступа

В результате первая версия структурной схемы ассоциативно настраиваемого бит-процессора приобретает вид рис. 3.14. В этой схеме, как и в Н1841 ВФ1, имеется 16-битный регистр инструкции, структура которой задана таблицей 3.7.

Для бит-процессора рис. 3.14 характерна утяжеленная двухступенчатая система дешифрации:

- при переходе от объектного кода к абсолютному коду (см. табл. 3.7), первый из которых используется при написании микропрограмм, а второй при формировании загрузочного модуля;

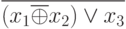

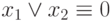

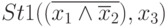

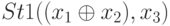

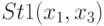

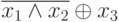

- при переходе от одного типа внешних связей бит-процессора (

соответствует

рис. 3.3-а) к другому типу связей (

соответствует

рис. 3.3-а) к другому типу связей (  соответствует рисункам 3.3-(б-д), когда за счет переименования входов-выходов меняются не только направления приема-передачи данных в бит-матрице, но и структура слова инструкции;

соответствует рисункам 3.3-(б-д), когда за счет переименования входов-выходов меняются не только направления приема-передачи данных в бит-матрице, но и структура слова инструкции; - при настройке на команду "расширенный транзит" меняются ролями поля: КОП и А 1 (см. табл. 3.7).

Разница в объектном и абсолютном коде негативно сказывается на динамике парирования отказов. Взаимозависимое (ассоциативное) декодирование различных полей слова инструкции резко увеличива ет аппаратные затраты на схемы дешифрации, задающие направления приема-передачи данных, и, что более важно, при микроэлектронной реализации нарушает регулярность всей схемы бит-процессора, что приводит к непропорциональному росту площади кристалла, занимаемой бит-процессором.

| Абсолютный код | Биты | Объектный код | Биты |

|---|---|---|---|

| Код операции (КОП) | 15-14 | Код операции (КОП) | 21-18 |

Управление (  ) ) |

13-12 | Адрес входа 1-го операнда | 17-16 |

| Управление входом (3) АЛУ | 11-10 | Адрес входа 2-го операнда | 15-14 |

| Управление входом транзита | 9-8 | Адрес входа 3-го операнда | 13-12 |

| Управление выходом АЛУ Управление выходом транзита | 7-6 5-4 | Адрес входа транзита Адрес выхода АЛУ | 11-10 9-8 |

| Управление выходом транзита | 3-2 | Адрес выхода транзита (1) | 7-6 |

| Признак задержки АЛУ | 1 | Адрес выхода транзита (2) | 5-4 |

| Тип внешних связей | 0 | Переименование вход-выход | 3-2 |

| Признак задержки АЛУ | 1 | ||

| Тип внешних связей | 0 |

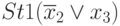

В схеме

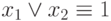

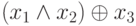

рис. 3.14 этот эффект проявляется в том, что при  поле регистра

поле регистра  инструкции используется для задания одной из конфигураций внешних связей рисунков 3.3-(б-д), а при

инструкции используется для задания одной из конфигураций внешних связей рисунков 3.3-(б-д), а при  поле

поле  управляет вторым выходом канала транзита. В результате при

управляет вторым выходом канала транзита. В результате при  схема

схема  должна принудительно адресоваться по выходу

должна принудительно адресоваться по выходу  полем

полем  ,чтобы в бит-процессоре реализовалась систолическая структура

рис. 3.3-б.

,чтобы в бит-процессоре реализовалась систолическая структура

рис. 3.3-б.

Как показал опыт эскизного схемотехнического и топологического проектирования бит-процессора рис. 3.14, такая ассоциативная дешифрация кода бит-инструкции внесла решающий вклад в 40%-ный рост аппаратных затрат (табл. 3.8) и увеличила занимаемую бит-процессором площадь в 1,7-1,8 раза по отношению к Н1841 ВФ1.

| Наименование блока | Н1841 ВФ1 | версия 1 | версия 2 |

|---|---|---|---|

| Регистр инструкции (КОП) | 88 | 44 | 66 |

| Регистр инструкции (коммутация) | 264 | 308 | 396 |

| Дешифратор АЛУ | 108 | 184 | 240 |

| Внутренняя коммутация | 64 | 96 | 96 |

| Операционные D-трштеры | 66 | 44 | 44 |

| АЛУ | 64 | 120 | 120 |

| Внешняя коммутация | 240 | 468 | 320 |

| Коммутационные D-триггеры | 66 | 88 | 88 |

| Средства управления АЛУ | 196 | 228 | 306 |

| Средства управления коммутацией | 264 | 308 | 396 |

| Объект управления канала АЛУ | 194 | 260 | 260 |

| Объект управления коммутацией | 306 | 556 | 408 |

| Итого на средства управления | 460 | 536 | 703 |

| Итого на объект управления | 500 | 816 | 668 |

| Итого на бит-процессор (БП) | 960 | 1352 | 1370 |

Взяв за основу структуру бит-инструкции в объектном коде (см. табл. 3.7), получим структурную схему бит-процессора 2-й версии (рис. 3.15) с системой команд табл. 3.9, которая содержит практически все активные "маскирующие" логические функции двух переменных: "И", "И - НЕ", "РАВНОЗНАЧНОСТЬ", "НЕРАВНОЗНАЧНОСТЬ", "ИЛИ - НЕ", "ИМПЛИКАЦИЯ", "НЕ - ИМПЛИКАЦИЯ".

В этой версии:

- под поле КОП выделено 3 бита, которые задают семь функций трех переменных, которых достаточно для получения методом "отождествления в ноль" одного из операндов всех функций Н1841 ВФ1 двух переменных и перечисленных выше "маскируюших" функций для реализации классических DD-ассоциативных конструкций [46];

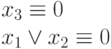

- все входные и выходные операнды бит-процессора коммутируются и управляются независимо, за исключением поля

, которое используется и для задания структуры внешних связей бит-процессора при

, которое используется и для задания структуры внешних связей бит-процессора при  ;

; - все еще требуется трансляция объектного кода в абсолютный, которая сопряжена с поиском незадействованных входов бит-процессора, для чего необходимо проводить анализ содержимого бит-инструкций соседних бит-процессоров.

Действительно, простейший способ выделения "незадействованно-го" входа состоит в определении "неадресуемого" выхода у четырех ближайших бит-процессоров. Но этот способ не подходит для периферийных бит-процессоров и не гарантирует полноты идентификации "незадейство-ванного" входа по результатам анализа кодов бит-инструкций ближайших ортогональных бит-процессоров. Объясняется это тем, что "незадейство-ванные" входы-выходы могут образовать достаточно длинные цепочки из D -триггеров каналов АЛУ и/или транзита, постоянно находящиеся

| № п/п | Количество операндов (  ) ) |

КОП | Условие) | Количество операндов (  ) ) |

№ п/п |

|---|---|---|---|---|---|

| 1 |  |

000 |  |

|

1 |

|

|

2 | |||

| 2 |  |

001 |  |

|

3 |

|

|

4 | |||

| 4 |  |

010 |  |

|

5 |

|

|

6 | |||

| 5 |  |

011 |  |

|

7 |

|

|

8 | |||

|

|

9 | |||

|

|

10 | |||

| Расширенный транзит | 100 | WTR | |||

| 6 |  |

101 |  |

|

11 |

|

|

12 | |||

| 7 |  |

110 |  |

|

13 |

|

|

14 | |||

| 8 | 111 |  |

15 |

в "нулевом" состоянии, причем вероятность образования такой цепочки тем выше, чем больше однородность микропрограммы и чем выше коэффициент использования внешних связей бит-процессора. Поэтому "радиус" анализа ближайших соседей имеет произвольную величину, а при включении в него периферийных бит-процессоров требуется дополнительная интерактивная процедура, которая в явном виде доопределяет входы бит-матрицы как неиспользуемых.

Отсюда, ассоциативная подстройка канала АЛУ на функцию двух переменных методом "фиксации в ноль" одного из трех входных операндов требует анализа бит-инструкций в произвольной окрестности по отношению к заданному бит-процессору, что по сложности решаемой задачи сопоставимо с анализом информационно-логических связей при классической компиляции программ.

Избавиться от такого рода проблем можно:

- введя третье состояние в D-триггеры регистров инструкций и во входные коммутаторы информационных каналов бит-процессора;

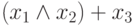

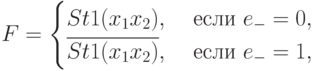

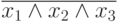

- заменив оператор ассоциативной подстройки канала АЛУ с "фиксации в ноль" (

) на "попарное отождествление"

(

) на "попарное отождествление"

(  ).

).

В обоих случаях состояние неиспользуемого входа АЛУ задается регистром инструкции собственного бит-процессора и не зависит от состояния выходов смежных бит-процессоров, причем первый способ приводит к еще большему увеличению аппаратных затрат и площади кристалла под бит-процессор, а второй способ снижает разнообразие реализуемых бит-процессором арифметико-логических функций (табл. 3.10).

| № п/п | Количество операндов (  ) ) |

КОП | Условие) | Количество операндов (  ) ) |

№ п/п |

|---|---|---|---|---|---|

| 3 |  |

010 |  |

|

1 |

|

|

2 | |||

| 2 |  |

001 |  |

|

3 |

|

|

4 | |||

| 1 |  |

000 | |||

| 4 |  |

011 |  |

|

5 |

|

|

6 | |||

| 5 | Расширенный транзит | 100 | |||

| 6 |  |

101 |  |

|

7 |

|

|

8 | |||

| 7 |  |

110 |  |

|

9 |

|

|

10 | |||

| 111 | - |  |

11 | ||

| 111 |  |

|

12 |

Сравнив табл. 3.9 и 3.10, можно убедиться:

- адаптивные возможности оператора отождествления переменных гораздо ниже, чем оператора фиксации в ноль одной из трех переменных;

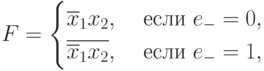

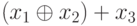

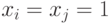

- практическая польза от порождаемых оператором отождествления переменных конечно-автоматных функций

и

и  (см. раздел 5.1 курса "Задачи и модели вычислительных наноструктур") еще требует экспериментального подтверждения;

(см. раздел 5.1 курса "Задачи и модели вычислительных наноструктур") еще требует экспериментального подтверждения; - для получения всего спектра функций табл. 3.9 необходимо расширить состав функций трех переменных табл. 3.10 и увеличить поле кода операции на 1 бит;

- структурно-функциональная схема бит-процессора рис. 3.15 пригодна для реализации обеих вариантов системы бит-инструкций, а изменения системы команд практически не сказываются на аппаратных затратах (см. табл. 3.8).

Анализ табл. 3.8 показывает:

- 2-я версия бит-процессора увеличивает аппаратные затраты на 42,7% по отношению к Н1841 ВФ1,что при двукратном сокращении числа бит-процессоров на реализацию конвейерного умножителя базовой операции обеспечивает аппаратный выигрыш почти в 1,4 раза;

- в бит-процессоре 2-й версии несколько хуже соотношение аппаратных затрат между объектом и средствами управления в сравнении с Н1841 ВФ1 (0,73 и 0,83 соответственно).

При оценке эффективности принимаемых технических решений в условиях расширения структурно-функциональных возможностей бит-процессоров более информативны удельные аппаратные затраты на одну арифметико-логическую и/или коммутационную функцию.