|

Добрый день!

Скажите, пожалуйста,планируется ли продолжение курсов по нанотехнологиям? Спасибо, Евгений

|

Методы и средства обеспечения живучести и восстановления работоспособности МКМД-бит-потоковых субпроцессоров

7.4. Особенности синтеза тест-данных и анализа откликов бит-процессоров

На время получения индивидуальных откликов от всех бит-процессоров тестируемого канала (в данном случае это  из (6.1) курса "Задачи и модели вычислительных наноструктур" основное влияние оказывают два фактора: режим работы бит-процессора и допустимое время "сеанса связи" с ним, которое определяется вторичной топологической структурой тестовой микропрограммы.

из (6.1) курса "Задачи и модели вычислительных наноструктур" основное влияние оказывают два фактора: режим работы бит-процессора и допустимое время "сеанса связи" с ним, которое определяется вторичной топологической структурой тестовой микропрограммы.

Из таблиц 5.7, 5.8 курса "Задачи и модели вычислительных наноструктур" и 3.1, видно, что бит-процессор может работать в трех режимах: комбинационного ( AND, NAND, XOR ), конечного ( ADD, ST1, CG ) и коммутационного ( WTR ) автомата с FIFO -регистровым типом распространения данных в процессе передачи, обработки или циклического "хранения" ( CG ).

В режиме конечного автомата "глубина" PD - ассоциативной обратной связи (см. рис. 5.12 и 5.13 курса "Задачи и модели вычислительных наноструктур") равна одному такту. Поэтому минимальная

последовательность тест-данных, в которой формируется декартово произведение второго порядка  , отвечающее полной матрице переходов такого автомата, имеет вид: 0,0,1,1,2,2,3,3,0,2,1,3,2,0,3,1,0.

, отвечающее полной матрице переходов такого автомата, имеет вид: 0,0,1,1,2,2,3,3,0,2,1,3,2,0,3,1,0.

Здесь  - десятичное представление наборов значений двоичных входных переменных бит-процессора:

- десятичное представление наборов значений двоичных входных переменных бит-процессора:  ,

,  ,

,  ,

,  .

.

Действующая карта отказов способна перевести бит-процессор из режима комбинационного в режим конечного автомата, что вынуждает использовать эту же последовательность и при диагностике "комбинационных" бит-инструкций.

При работе в режиме коммутационного автомата используются только D -триггеры канала АЛУ и транзита, полная матрица переходов которых задана на алфавите  и формируется последовательностью 0,0,1,1,0.

и формируется последовательностью 0,0,1,1,0.

В Т -рекурсивных тестах слияние по "ИЛИ" откликов от всех бит-процессоров одного тестового канала и продолжительность "сеансов связи" с каждым из них, которая ограничена 4 тактами (см. рис. 7.12- 7.14), приводят к следующим разбиениям на циклы и модификациям этих последовательностей тест-данных:

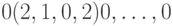

- для бит-операций AND, XOR, ADD:

;

;  ;

;  ;

;  ;

;  , где выход канала АЛУ протестированного бит-процессора устанавливается в "ноль" комбинацией тест-данных

, где выход канала АЛУ протестированного бит-процессора устанавливается в "ноль" комбинацией тест-данных  ;

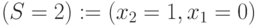

; - для бит-операции ST1:

;

;  ;

;  ;

;  ;

;  , где выход канала АЛУ протестированного бит-процессора устанавливается в "ноль" комбинацией тест-данных

, где выход канала АЛУ протестированного бит-процессора устанавливается в "ноль" комбинацией тест-данных  ;

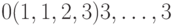

; - для бит-операции NAND:

;

;  ;

;  ;

;  ;

;  , где выход канала АЛУ протестированного бит-процессора устанавливается в "ноль" тестовой комбинацией

, где выход канала АЛУ протестированного бит-процессора устанавливается в "ноль" тестовой комбинацией  ;

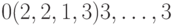

; - для бит-операции WTR (см. рис. 3.3 и 7.10):

;

;  , где "сеанс связи" с тестируемым бит-процессором ограничен 3 тактами;

, где "сеанс связи" с тестируемым бит-процессором ограничен 3 тактами; - для бит-операций NOP, CG и шагов 1 и 2 в части динамики работы D -триггеров:

;

; - при контроле начального состояния D -триггеров FIFO -регистровой D -шины:

, так как все бит-процессоры находятся в режиме "прослушивания" этих состояний.

, так как все бит-процессоры находятся в режиме "прослушивания" этих состояний.

Здесь:

- тестовая (под)последовательность, отвечающая каждому циклу(?) диагностики фиксированной бит-инструкции, заключена в скобки;

- предшествующий скобкам "0" отвечает правильному начальному состоянию FIFO -регистровой D -шины, передающей тестовую (под) последовательность;

- символы после скобок отвечают условиям правильного распространения тестовой (под)последовательности и откликов по FIFO -регистровой D -шине.

Специфика работы тестовых микропрограмм при контроле бит-инструкций:

- NAND связана с необходимостью DD -ассоциативной "блокады" паразитных "единичных" откликов от нетестируемых в данный момент времени бит-процессоров одного канала, что реализуется бит-процессорам 2-й строки этого канала;

- CG связана с тем, что "отклик" каждого бит-процессора тестируемого канала заносится в их регистры бит-инструкций при программировании бит-матрицы и циклически "хранится" в них; это требует не только DD -ассоциативной "блокады", но и соответствующего сдвига влево хранимой тестовой последовательности, которая представлена в шестнадцатеричном виде в мнемонической записи этой бит-инструкции;

- NOP связана с тем, что в этом случае доступ к таким бит-процессорам по входу-выходу можно осуществить только слева, что выполнимо только по вертикальным Т -каналам передачи тест-данных и откликов. На основе проведенного анализа основных факторов, определяющих

динамику работы подсистемы локализации и идентификации отказов в современных микроэлектронных МКМД-бит-потоковых технологиях, можно сделать следующие выводы.

- При синтезе тестовых последовательностей проверяемые бит-процессоры приходится рассматривать как конечные, а не как комбинационные автоматы.

- Провести полное тестирование даже "высоконадежных" (сверх) параллельных МКМД-бит-потоковых вычислителей невозможно в принципе, а для поддержания достоверности гипотез, снижающих размерность задач локализации и идентификации, требуются специальные меры защиты "рабочего тела" в процессе его изготовления и эксплуатации.

- В процессе тестирования относительно больших бит-матриц нарушается системо- образующее для МКМД-бит-потоковых технологий неравенство (6.1) курса "Задачи и модели вычислительных наноструктур", что при коротком "времени жизни" может привести к зацикливанию супрамолекулярного вычислителя на фазе диагностики. Для восстановления соотношений в неравенстве (6.1) курса "Задачи и модели вычислительных наноструктур" требуется обеспечить прямой доступ по P - и D -шинам к каждому бит-процессору.

- Tlr -адаптивность тестовых микропрограмм является вынужденной мерой, обусловленной использованием параметрических методов адаптации однородной бит-матрицы под требования активизированного поток-оператора пользователя.

- Восстановление работоспособности МКМД-бит-потоковых субпроцессоров можно провести в интерактивном режиме, допускающем перекомпоновку тела микропрограммы не только на основе аффинных преобразований, что требует использования в эксплуатации отладочных средств разработчика, таких как имитатор работы бит-матрицы и графический редактор (см. рис. 7.2).

7.5. Особенности термального синтеза тестовых микропрограмм в процессе эксплуатационной диагностики

Согласно методике многоуровневого имитационного моделирования бит-потоковых субпроцессоров (см. раздел 3.4), во время функционального контроля пространство прямой диагностики бит-процессоров разбивается на три подпространства:

- подпространство микропрограммного управления бит-процессоров, образованное регистрами команд и глобальной шиной управления вводом программы, которое поддерживает условия требуемого пространственно-временного, регистрового взаимодействия бит-инструкций активизированного поток-оператора пользователя;

- подпространство внутренней системы коммутации бит-процессоров, которое описывает всевозможные состояния входных и выходных коммутаторов бит-процессоров, обеспечивающих пространственно-временное распределение потоков данных;

- подпространство арифметико-логических функций бит-процессоров, образованное всевозможными состояниями АЛУ, которое обеспечивает пространственно-временное взаимодействие потоков данных и сигналов.

Таким образом, стратегию функционального иерархического контроля можно реализовать как взаимосвязанную систему тестов, в которой поэтапно сужается проверяемое пространство возможных состояний бит-матрицы за счет информации, полученной на предыдущих этапах тестирования.

В СБИС Н1841 ВФ1 каналы ввода и хранения бит-инструкций выполнены по простейшей последовательной схеме, что было обусловлено количеством выводов в корпусе СБИС. Это увеличило время ввода (микро)программы, но позволило достаточно просто проконтролировать правильность ее загрузки в 320-битный FIFO -регистр. Для этого достаточно осуществить двойной ввод (микро)программы и сопоставить на выходе загружаемую последовательность с получаемой после первого ввода. Это достаточно достоверный способ обнаружения отказов D -триггеров, но он не позволяет отреагировать на сбои во время второго сеанса ввода (микро) программы.

В системе параллельного ввода (микро)программы рис. 7.19 время ввода сокращено в 16 раз, но усложнена процедура контроля правильности ввода, так как нет возможности напрямую считывать реально хранимую бит-инструкцию в каждом регистре бит-инструкции. В этом случае подпространство управления можно тестировать только косвенно в процессе контроля коммутационных и функциональных возможностей бит-матрицы, которые в регистрах бит-инструкций представлены различными полями (см. рис. 3.2).

При контроле вертикальных и горизонтальных связей косвенно проверяются D -триггеры, принадлежащие поля А1-А6 регистра бит-инструкций. Поэтому тестовые микропрограммы контроля вертикальных и горизонтальных связей необходимо модифицировать таким образом, чтобы каждый из этих триггеров побывал и в "нулевом", и в "единичном" состояниях.

Аналогичным образом косвенно проверяется работоспособность D -триггеров, принадлежащих полю кода операции регистра бит-инструкций, когда во время тестирования арифметико-логических функций необходимо делать вывод о неработоспособности либо АЛУ, либо регистра. Это делает весь процесс эксплуатационного контроля бит-матрицы глобально связанным, что негативно сказывается на продолжительности коммутационного и функционального контроля бит-матрицы и служит достаточно серьезным препятствием на пути построения такой системы взаимного контроля бит-матриц, в которой вопрос "кто сторожит сторожа" стоял бы не так остро.

По результатам косвенной проверки пространства управления трудно получить достаточную информацию о характере неисправности бит-процессора и о количестве одновременных отказов, так как отказ одного или двух вентилей в бит-процессоре не выводит его из строя, а лишь сокращает пространство (  ) правильно исполняемых инструкций.

) правильно исполняемых инструкций.

Поэтому имеет смысл организовать доступ к регистрам бит-инструкций для непосредственного контроля пространства управления по схеме рис. 7.19, где:

- вход SetPr используется для выделения бит-процессора как при записи в его регистр команды соответствующей бит-инструкции, так и при ее "чтении" в процессе тестирования канала управления бит-матрицей;

- вход Progrвх используется для записи потока 16-разрядных бит-инструкций микропрограммы;

- вход SetTst используется для установки режима тестирования регистров бит-процессоров;

- выход TstPrg поочередно предоставляется для "чтения" контролируемой в данный момент времени бит-инструкции;

- вход C служит для подачи сигнала синхронизации.

Рис. 7.19. Схема бит-процессора с доступом для контроля подпространства микропрограммного управления

Из перечисленных сигналов глобальными являются SetTs и C, и именно они ограничивают размеры синхронно работающей бит-матрицы.

Схема рис. 7.19 работает следующим образом. Сначала за 1 такт в регистр команды бит-процессора, выделенного с помощью сигнала SetPr, заносится бит-инструкция, а в остальные бит-процессоры заносятся нули. После этого в течение 16 тактов подается сигнал SetTst = 1 и регистры команд всей матрицы начинают работать как сдвиговые регистры. Но так как во все регистры, кроме тестируемого бит-процессора, внесены нули, то записанная инструкция считывается на выходе TstPrg последовательно старшим разрядом вперед. Общее время диагностики подпространства управления  равно

равно ![T_d^u = [8\cdot(М_{1} *М_{2})^{2} +24\cdot М_{1} *М_{2}]\cdot\tau,](/sites/default/files/tex_cache/f16dfd0b16078ac9990b7c891b0977b7.png) (должно быть

(должно быть  ), что при тактовой частоте бит-матрицы 250 МГц и ее размерах

), что при тактовой частоте бит-матрицы 250 МГц и ее размерах  составит 83 миллисекунды.

составит 83 миллисекунды.

Возможны и другие варианты построения схем бит-процессоров с доступным для тестирования подпространством управления, которые минимизируют системные временные издержки этого этапа диагностики за счет схемотехнического уровня организации работы бит-матрицы. Конкретный вариант схемы управления "записью-чтением" регистров команд бит-процессоров зависит от разбиения всего пространства управления на две составляющие, контролируемые прямым и косвенным путем. Поэтому в первую очередь необходимо оценить все системные аппаратно-временные издержки на функциональный контроль и контроль коммутации, и только после этого приступать к их минимизации, вводя в схему бит-процессора дополнительные элементы для эффективного контроля регистров бит-инструкций.

При выборе подпространства прямой диагностики внутренней системы коммутации бит-процессоров следует учесть, что отобранные кодовые комбинации тестируемых бит-инструкций кроме всего прочего должны обеспечить опосредованный информационный доступ к каждому бит-процессору. Только при выполнении этого условия можно организовать из последовательности бит-процессоров общий канал распространения тест-данных и откликов от периферии к центру бит-матрицы и наоборот (в дальнейшем тестовый канал ).

Выделить подпространство коммутации, контролируемое прямым путем, можно с помощью упрощающей гипотезы: если в процессе прямой диагностики бит-матрицы каждый бит адресной части (А1-А6, рис. 3.2) всех бит-инструкций побывал и в "нулевом", и в "единичном" состоянии, то результаты прямого контроля полученных таким путем коммутационных функций бит-процессоров с высокой степенью достоверности можно распространить на остальные, косвенно контролируемые комбинации соединения входов-выходов.

В этом случае для прямого контроля коммутационных возможностей бит-матрицы требуется всего два типа тестовых микропрограмм, которые к тому же обеспечивают контроль вертикальных и горизонтальных каналов FIFO -регистровой передачи данных по бит-матрице, а значит, и правильность исполнения в ней операции "расширенный транзит" ( WTR - см. табл. 3.1) [138-141]. Для такого тестирования достаточно закодировать термы, изображенные на рис. 7.20, следующим образом:

Для рис. 7.20-а пары адресов (А1-А4) кодируют канал передачи бит-данных "слева-направо", (А2-А5) - "справа-налево", а (А3-А6) -

"слева-налево", а для рис. 7.20-б все аналогично, только с вращением вдоль побочной диагонали [298]. Аналогично для соответствующих пар рис. 7.20 (в-г), (д-е), (ж-з), (и-к), (л-м).

Таким образом, контроль подпространства коммутации можно совместить с контролем подпространства управления в части управления входными и выходными коммутаторами и определяет характер расположения интерфейса ввода-вывода бит-матрицы. Для удобства тестирования интерфейс должен быть полностью доступен (см. рис. 7.18) либо слева и снизу при термальном составе рис. 7.20-а и 7.20-б, либо сверху и справа при термальном составе рис. 7.20-в и 7.20-г.

В этом случае контроль подпространства коммутации и связанного с ним подпространства управления можно ограничить двумя типами однострочных тестов [138-141] (на рис. 7.20 верхняя строка - это первый тип, а нижняя - это второй тип), которые снижают размерность тестируемого пространства состояний регистра бит-инструкций бит-процессора с 216 до 9:

- два типа организации тестовых каналов необходимо использовать при контроле коммутации, которые имеют два типа модификации признака задержки: ПЗ = 0 и ПЗ = 1 (итого 4 типа тестов для контроля коммутационных возможностей бит-матрицы);

- пять типов тестов контроля бит-инструкций АЛУ: ADD, ST1, XOR, AND, NAND (см. табл. 3.1), число которых можно сократить до трех: ADD - КОП = 001, ST1 - КОП = 110 и XOR - КОП = 101, с учетом "вложенности" функций в АЛУ, реализованного по схеме УЛМ (см. рис. 5.12 и 5.13 курса "Задачи и модели вычислительных наноструктур").

Таким образом, при контроле бит-матрицы тестовое ядро прямой оперативной диагностики можно ограничить семью состояниями регистра команд каждого бит-процессора из 216 возможных. При этом повысить полноту диагностики всей бит-матрицы можно в процессе послеполетного обслуживания ЛА. Цель такой диагностики состоит в построении и анализе матрицы трансформаций функций под воздействием карт отказов, которую можно использовать при интерактивной компоновке "рабочего тела" микропрограммы, учитывающей топологию размещения бит-инструкций, фактически реализуемых бит-процессорами с отказавшими вентилями.