Освоение средств разработки

Разработка исходного кода

Для описания аппаратных схем удобно использовать специально разработанные для описания поведения аппаратуры языки, как VHDL, Verilog, System Verilog. В этих языках выполняется описание поведения на уровне отдельных регистров и передач сигналов между ними - т.н. RTL - уровень регистровых передач.

Исходный код (VHDL):

if (Clk = '1' and Clk'EVENT) then If (X = '1') then Y <= A and B; else Y <= not(A or B) xor C; end if; end if;

Исходный код (Verilog):

always@(posedge Clk) if (X = 1) Y <= A & B; else Y <= ~(A | B) ^ C; end

На данном этапе разработки на языках описания аппаратуры реализуются выбранные, разработанные ранее алгоритмы, протоколы, спецификации. В процессе разработки выполняется проверка работоспособности кода с помощью программных симуляторов, входящих в состав САПР, или с помощью отладочных плат с ПЛИС.

К наиболее популярным САПР относятся Vivado(Xilinx), Quartus (Intel/Altera).

Vivado Design Suite - это программный пакет, созданный Xilinx для синтеза и анализа конструкций, написанных на языках семейства HDL - описания аппаратуры hardware description language (HDL), представляет собой интегрированную среду проектирования (IDE), построенными на общей масштабируемой модели данных и общей среде отладки.

В состав входят компилятор, симулятор и интегратор IP для быстрого конфигурирования и встраивания в проект IP ядер из предоставляемого набора библиотек; так же имеется подсистема хранения и исполнения сценариев на языке TCL для расширения возможностей среды.

Создаваемое RTL-представление представляет собой конечный автомат (то есть схему, выполненную в синхронном стиле, что предпочтительно для современных FPGA), управляющий потоками вычислений. Результаты зависят от проектных ограничений (constraints), а также, причем в большой степени, от директив компилятора. Директивы также могут облегчить формирование интерфейсов создаваемого модуля: он может быть экспортирован в виде IP-ядра с интерфейсом, определенным пользователем, но также можно указать на необходимость его экспорта в виде периферийного модуля для шины AXI4 (для установки в процессорную систему) или модуля для инструмента System Generator for DSP.

Логический синтез

На следующем этапе разработки логика работы преобразуется в описание на вентильном уровне.

Логическое выражение после синтеза:

DFF.D <= (X and (A and B)) or (not(X) and (not(A or B) xor C)); Y <= DFF.Z

Схемные примитивы (рисунок 3.1):

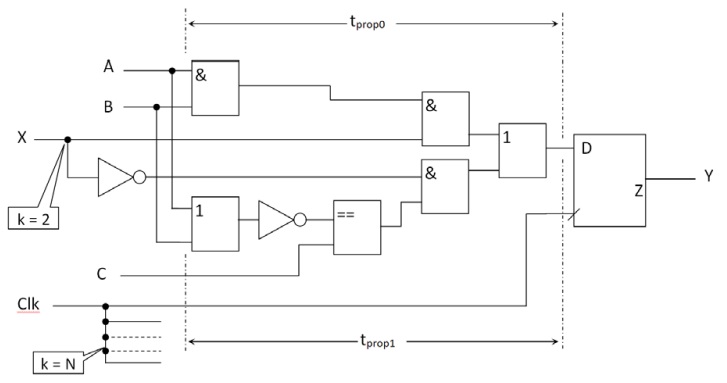

Схемное представление логики исходного кода ( рисунок 3.2):

где k - коэффициент разветвления для цепи, а  - время распространения сигнала по ветвям логики 0 и 1 соответственно.

- время распространения сигнала по ветвям логики 0 и 1 соответственно.

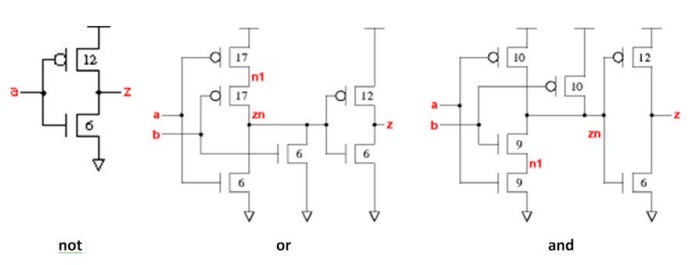

Поэлементное представление примитивов ( рисунок 3.3):

Компилятор - инструмент для представления логики проекта на вентильном уровне. Он предоставляет богатый набор функций для автоматизации проектирования, как в схемном, так и в топологическом представлениях, и интерфейс с инструментами моделирования.

Собственно, синтезатор - инструмент логического синтеза, предназначенный для трансляции и оптимизации схемы из описания на уровне RTL в список цепей (netlist) на уровне стандартных ячеек (транзисторной, вентилей).

В современном проекте СнК в каждом логическом блоке (модуле), не считая макроблоков и памяти, могут содержаться миллионы логических вентилей. Объём синтеза и оптимизации, который должен выполнить синтезатор, очень большой. Необходимо собрать логическую схему и оптимизировать ее по ряду параметров, таких как быстродействие, динамическое и статическое энергопотребление, площадь и т.д. Дополнительные сложности связаны с необходимостью учета планировки кристалла, а также того факта, что оптимизация должна проводиться во всех режимах работы блока одновременно.

Инструмент допускает распараллеливания вычислений на нескольких ядрах.

Во многих современных проектах при разработке топологии инженеры сталкиваются с задачами трассируемости цепей. Часто данные проблемы возникают из-за высокой локальной связности логических элементов в критических цепях. В синтезаторах, как правило, присутствует алгоритм оптимизации, который минимизирует количество необходимых проводников и их локальных пересечений с учетом планировки и размещения, решая, таким образом, обозначенные выше задачи.

Синтезаторы обычно встроены в мощные пакеты САПР, но есть и выполненные в виде отдельных программных продуктов:

Встроенные (как часть пакета разработки от изготовителя FPGA): Lattice Synthesis Engine (Lattice), Quartus Synthesis (Intel/Altera);

Отдельные (предлагаемые как отдельные решения, не привязанные к единственной архитектуре): Design Compiler, FPGA Compiler (Synopsys), Precision Series, Leonardo Spectrum (Siemens).

Верификация

На этом этапе проводится проверка соответствия RTL кода исходным алгоритмам и спецификациям. Проверки соответствия выполняются в нескольких направлениях, многократно, на разных уровнях иерархии, поэтому этап требует привлечения нескольких САПР.

Поведенческая верификация выполняется на симуляторах с возможностью параллельной работы. Обеспечивает работу на уровне регистровых передач (RTL) и на вентильном уровне. Может использоваться при разработке тестирующего окружения (DFT). Обычно САПР для верификации использует методологию UVM - Universal Verification Methodology, может выполнять симуляцию для проектов с низким уровнем потребления, со смешанными сигналами (цифровые + аналоговые). Тестирование может проводиться и на уровне кристалла и на уровне отдельных IP блоков, тесты обычно формируются на языках SystemVerilog/UVM, SystemC. По результатам формируется база данных из результатов симуляции, верификации по различным метрикам, результатов анализа покрытия тестами.

Примеры САПР: Xcelium (Cadence), QuestaSim.

Формальная верификация - инструмент оценки соответствия RTL- описания блока заданной формальной логической модели. Статический анализ на основе математических методов теории доказательств дает возможность провести исчерпывающую проверку логики работы блока и сравнить её с формальными требованиями.

Проверки выполняются с помощью механизма предположений (утверждений - Assert). Этот механизм позволяет проверить заданное разработчиком условие. Например, в блоке HDL-кода можно вставить проверку состояния внутренних переменных, которая постоянно будет выполняться в процессе моделирования. Использование встроенных утверждений позволяет увеличить наблюдаемость проекта при моделировании, быстрее и легче локализовать источник ошибки, поскольку проверки делаются непосредственно по месту. Кроме того, встроенные утверждения очень полезны в методах формальной верификации. Встроенные утверждения отражают то, что мы ожидаем от устройства, как оно должно работать. Непосредственно в утверждении может быть определено как правильное, так и неправильное поведение компонентов устройства (RTL-блоки, интерфейсные блоки и блоки управления). Таким образом, можно контролировать и правильность поведения схемы, и возникновение запрещенных ситуаций.

Примеры САПР: JasperGold.

Вопросы для самостоятельной работы

В качестве практической работы рекомендуется проведение самостоятельной отработки элементарных навыков на готовом проекте демонстрационного примера. Для этого рекомендуется открыть проект чистого Кузнечика (архивный файл gstdr3432015_apbctr_ahbdflow_tb_struct.rar) и выполнить доработку кода проекта: дописать счётчик записей ключа, отсинтезировать, модифицировать тестбенч, запустить моделирование, получить временные диаграммы.