Проект Larrabee

Архитектура Larrabee [36-38] оптимизирована для повышения общей производительности высокопроизводительных систем за счет следующих возможностей:

- параллелизм на уровне данных и задач (векторные вычисления и организация потоков);

- нет необходимости переформулировать задачи для использования регулярных форм/алгоритмов;

- повышение эффективности программирования за счет поддержки программных моделей IA;

- применение технологии явного параллелизма на уровне команд (EPIC — Explicitly Parallel Instruction Computing);

- применение предикатных вычислений.

В сочетании с новым уровнем спекулятивных вычислений это значительно уменьшает количество условных переходов и, соответственно, ошибочных предсказаний направления переходов. В свою очередь, применение EPIC однозначно диктует появление в архитектуре большого числа функциональных устройств и сверхбольших файлов регистров.

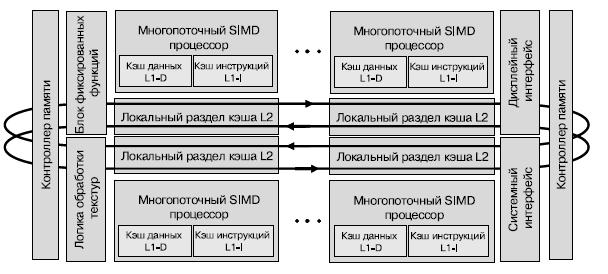

В своем составе процессор Larrabee содержит контроллеры памяти, блок настраиваемой логики, блок фиксированных функций, системный интерфейс и набор вычислительных ядер, каждое из которых является IA-процессором [37].

Ядра соединены между собой двусторонней кольцевой шиной, в которую также включены и остальные функциональные блоки контроллера ( рис. 6.1). Ядрам обеспечен быстрый доступ к памяти, к блоку фиксированных функций и когерентность кэшей.

В Larrabee имеется кэш первого и второго уровней. Кэш первого уровня входит в состав ядра. На один аппаратный поток приходится 8 Кб кэша команд и 8 Кб кэша данных; таким образом, размер кэша одного ядра составляет 64 Кб.

Кэш второго уровня (L2) распределен между ядрами — это ускоряет обмен данными между ядрами, облегчает репликацию и общее использование данных.

Кэш второго уровня расположен отдельно от ядер, разделами — по одному на ядро. Каждое ядро имеет быстрый доступ к своему разделу кэша второго уровня. Размер локального раздела кэша второго уровня — 256 Кб. Все кэши второго уровня соединены внутренней кольцевой шиной, которая используется для обеспечения когерентности данных при записи. Как и в современных процессорах Intel, в Larrabee поддерживаются спецкоманды для работы с кэшем. Они включают команды предвыборки (prefetching), т. е. явной загрузки данных из ОЗУ в кэш 1-го или 2-го уровня, а также команды смены приоритета кэш-линии. Последнее может применяться при последовательной обработке массивов. Снижение приоритета вновь загруженных данных позволяет избежать замусоривания кэша и повысить производительность. Использование традиционной схемы кэширования, в отличие от явно адресуемой памяти, как в CELL, было вызвано двумя причинами: во-первых, можно применять кэш в алгоритмах с более сложными схемами доступа к памяти, например, при трассировке лучей; во-вторых, кэш позволит не терять производительность на уже существующих программах.

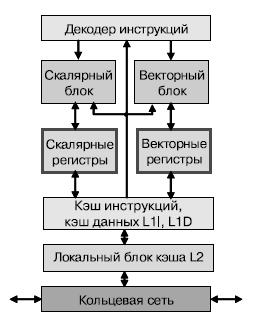

Каждое ядро, как было упомянуто, является процессором архитекту- ры IA, имеет когерентный кэш, систему виртуальной адресации и поддер- живает вытесняющую многозадачность.

При разработке вычислительного ядра за основу был взят процессор P54C с архитектурой x86. Из него исключили функциональность исполнения программы с внеочередным выполнением команд, что позволило значительно сократить площадь, занимаемую на кристалле одним ядром. Это позволяет разместить на кристалле большее число ядер и повысить общую производительность системы.

Larrabee поддерживает возможности, характерные для современных процессоров на базе архитектуры x86, в частности, 64-разрядные расширения и команды для эффективной работы с кэшем. Поддерживаются также некоторые специальные команды, например, команда побитового сканирования содержимого регистра с определением первого бита со значением 1.

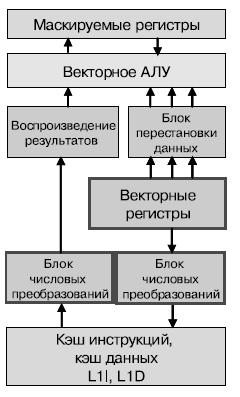

Ядро [38] имеет 32 512-битных векторных регистра, поддерживает полный набор векторных операций при работе с целыми данными и с данными в формате с плавающей точкой одинарной и двойной точности:

- mul, add, sub, adc, sbb, subr, and, or, xor, multiply-add, multiply-sub;

- векторное сравнение;

- операции чтения/записи с различными выравниваниями;

- операции сборки/разборки;

- битовые манипуляции.

Система команд содержит трехоперандные команды. Команда за- грузки Load может выбирать аргумент напрямую из памяти. Беззатратное преобразование типов:

- все математические операции осуществляются с 32- и 64-битными данными;

- расширение данных при загрузке из памяти;

- сжатие / обратное преобразование при помещении в память;

- поддерживаются практически все типы данных DX/OpenGL, включая float16, unorm8 и подобные.

Ядро имеет систему предсказания ветвлений.

Вычислительные ядра имеют полную поддержку вычислений стандарта IEEE (fast SSE). При вычислениях не проводится денормализация ( DAZ+FTZ always on). Всегда идет округление до ближайшего числа. В целях уменьшения занимаемой ядром площади (уменьшение размеров ядра) нет поддержки обработки исключительных ситуаций.

Поддерживаются инструкции Inf, NaN, signed 0. Инструкция Madd не производит промежуточных округлений.

Система команд векторного вычислительного блока [38] ( рис. 6.3) включает команды с целыми типами данных, а также с вещественными типами данных с одинарной и двойной точностью. Одно векторное ФУ способно исполнять до двух команд за такт.

Команда векторной загрузки данных из памяти трактирует свой операнд как векторный регистр, каждый компонент которого задает 32-разрядный адрес в памяти, и загружает данные по этим адресам. В случае когерентности адресов это позволяет значительно сократить накладные расходы на доступ к памяти. Подобная команда очень полезна для программ, использующих сложные и неравномерные структуры данных. На тестах, проведенных Intel, применение этой команды позволяло достигать троекратного увеличения производительности при работе с нерегулярными структурами данных.

С учетом системы команд ВФУ, одно ядро может использоваться для одновременной обработки нескольких (до 16) логических шейдерных потоков одновременно, при этом управляющие структуры могут моделироваться при помощи регистра маски. Альтернативный вариант — рассматривать Larrabee как векторный процессор и применять его соответствующим образом.

Ядра Larrabee поддерживают аппаратную многопоточность, по аналогии с технологией Hyper Threading в современных ГПУ, и позволяет частично решить проблему дисбаланса производительности памяти и процессора. Если один из потоков простаивает, выполняя операцию с памятью или кэшем, исполняются команды другого потока, сокращая время простоя центрального процессора. Одно ядро Larrabee поддерживает одновременно до 4 аппаратных потоков, каждый из которых имеет свой набор регистров. На каждый поток выделяется по 8 Кб кэша инструкций и 8 Кб кэша данных.

Скалярное вычислительное устройство Larrabee имеет два конвейера. Как и во многих других процессорах компании Intel, в которых используется такое решение, первый конвейер может выполнять любые команды, а второй — только часть команд. Задача выбора правильного порядка команд возлагается на компилятор, поскольку Larrabee не поддерживает внеочередное выполнение команд. Выбор подмножества команд для второго конвейера был обусловлен, с одной стороны, минимизацией площади второго конвейера на чипе, с другой — минимизацией нагрузки на компилятор по правильному упорядочиванию команд.

Основным отличием ядра Larrabee от других процессоров Intel является использование векторных команд с обработкой большого числа данных. Один операнд векторной команды имеет размер 512 бит, или 16 вещественных чисел с одинарной точностью. Такой же размер имеют векторные регистры. Более традиционные процессоры Intel поддерживают векторные команды с обработкой 4 значений с одинарной точностью (128 бит). Более широкий размер операнда векторной команды позволяет повысить производительность исполнения шейдеров при снижении общей площади ядра на кристалле. Векторное ФУ дает наибольший вклад в вычислительную мощность Larrabee, его применение является ключом для достижения высокой производительности на реальных задачах.

Модель программирования Larrabee поддерживает модель программирования для х86-й архитектуры. Общим для программирования Larrabee является использование компилятора С/С++, который статически компилирует программы для набора инструкций Larrabee x86. Многие С/С++-приложения могут быть скомпилированы для данного процессора и могут работать корректно без модификации. Такое положение дел благоприятно для портирования приложений, связанных с интенсивными вычислениями. Два основных ограничения лежат в области вызовов системных приложений и архитектуры драйверов устройств, которые нуждаются в перекомпиляции или модернизации.

Основные аспекты программирования для Larrabee — программные потоки (многопоточное программирование), векторизация и использование SIMD, коммуникации между хост-системой и Larrabee. Все векторные блоки процессора являются полностью программируемыми.

Многопоточное программирование основано на расширении известной модели POSIX Thread API, позволяя привязывать нити программы к конкретным аппаратным нитям или ядрам. Для снижения накладных расходов при переключении потоков в многопоточных приложениях предусмотрена оптимизация потоков. Реализация многопоточного программирования для Larrabee возможна при использовании Intel Thread Building Blocks, поддерживается модель OpenMP. Все эти возможности поддерживаются компилятором Larrabee Native’s C/C++.

Компилятор Larrabee Native’s C/C++ включает в себя версию технологии Intel’s autovectorization. Векторные устройства могут быть запрограммированы векторными инструкциями С++ или прямыми ассемблерными вставками.

В решениях, основанных на центральном процессоре и карте расширения с Larrabee, Larrabee может управляться драйвером операционной системы для платформы. В подобных платформах двоичный код Larrabee тесно связан и перемешан с кодом хост-процессора.

Краткие итоги

Процессор Larrabee представляет собой совокупность вычислительных ядер х86-совместимой архитектуры, которая оптимизирована для решения многопоточных задач, связанных с обработкой графических эффектов, физических эффектов, векторных вычислений.

Заявленная совместимость с архитектурой x86 открывает неплохие возможности по переносимости приложений и расширению их функциональности.

Контрольные вопросы

- Из каких основных блоков состоит процессор Larrabee?

- Опишите структуру вычислительного ядра процессора Larrabee.

- Опишите структуру векторного сопроцессора.

- Какие модели программирования поддерживает процессор Larrabee?

Упражнения

- В соответствии с моделью программирования распишите один из известных вам алгоритмов численного интегрирования.

- Проделайте аналогичные построения для цифрового фильтра с бесконечной импульсной характеристикой (БИХ-фильтр).