|

Здравствуйте Владимир (Ефименко). Я обучаюсь по программе повышения квалификации "Наноэлектронная элементная база информатики на основе полупроводников и ферромагнетиков". У меня проблема с тестом № 2 (к лекции № 2) по этой программе. Я несколько раз пытался пройти этот тест, но больше 50 баллов набрать не удаётся, хотя я всё делаю в соответствии сматериалом лекции. В заданиях этого теста есть ошибки, которые видны невооружённым глазом. Обращаюсь к Вам как к инспектору этой программы повышения квалификации. Найдите возможность исправить ошибки в тесте № 2. Из-за остановки на этом тесте я не могу двигаться дальше, а у меня очень ограниченное время на освоение этой программы. Заранее благодарен Вам за внимание к моим проблемам и помощь. |

Наноэлектронные устройства памяти на кремниевых КМДП транзисторах

Организация и работа "NAND" флеш-памяти

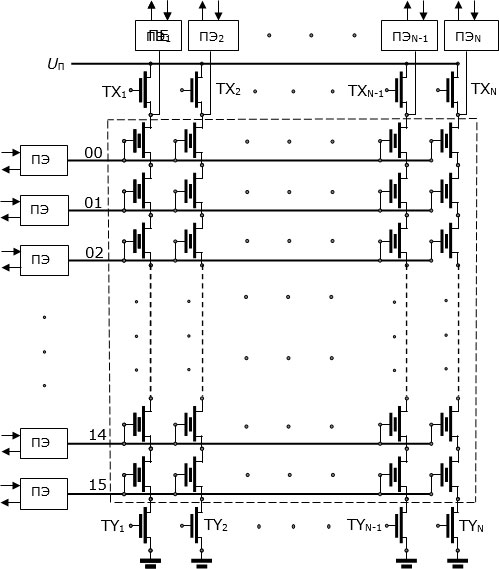

На рис. 6.9 показана схема организации матриц флеш-памяти типа "NAND". Как и в предыдущей схеме, матрица выделена штриховой рамкой, а управляющие затворы всех ячеек памяти, размещенных в одной строке, присоединены к общей горизонтальной шине. Потенциал на ней задается соответствующей периферийной электроникой строки (ПЭ).

Транзисторы всех ячеек памяти, расположенных в одном столбце, соединены здесь последовательно. Вместе с  -канальным транзистором

-канальным транзистором

-канальные транзисторы ячеек памяти, расположенных в одном столбце, образуют КМДП логическую схему NAND (вспомните

рис.

5.7 из

"Наноэлектронная элементная база информатики на кремниевых КМДП транзисторах

"

). Отсюда и название данного варианта организации флеш-памяти. Действительно, низкий потенциал на входе соответствующей периферийной схемы

-канальные транзисторы ячеек памяти, расположенных в одном столбце, образуют КМДП логическую схему NAND (вспомните

рис.

5.7 из

"Наноэлектронная элементная база информатики на кремниевых КМДП транзисторах

"

). Отсюда и название данного варианта организации флеш-памяти. Действительно, низкий потенциал на входе соответствующей периферийной схемы

-го столбца устанавливается лишь тогда, когда все транзисторы этого столбца открыты.

-го столбца устанавливается лишь тогда, когда все транзисторы этого столбца открыты.

В режиме считывания согласно заданному адресу на выбранную горизонтальную шину, например, на шину 00...01, подается потенциал считывания  (см.

рис.

6.6). На другие горизонтальные шины, в отличие от предыдущей схемы, подается потенциал, существенно выше, чем

(см.

рис.

6.6). На другие горизонтальные шины, в отличие от предыдущей схемы, подается потенциал, существенно выше, чем  , при котором все транзисторы столбца, независимо от заряда, занесенного на их плавающие затворы, открыты. Если на плавающем затворе выбранного транзистора имеется отрицательный электрический заряд (записана логическая "1"), то этот транзистор остается закрытым, и на вход соответствующей периферийной схемы

, при котором все транзисторы столбца, независимо от заряда, занесенного на их плавающие затворы, открыты. Если на плавающем затворе выбранного транзистора имеется отрицательный электрический заряд (записана логическая "1"), то этот транзистор остается закрытым, и на вход соответствующей периферийной схемы  действует высокий потенциал.

Это означает считывание "1", если, конечно, соответствующая вертикальная шина через ключевой транзистор

действует высокий потенциал.

Это означает считывание "1", если, конечно, соответствующая вертикальная шина через ключевой транзистор  подключена к источнику питания. Если же на плавающем затворе выбранной ячейки памяти отрицательного электрического заряда нет (записан логический "0"), то этот транзистор тоже открыт, и на вход соответствующей периферийной схемы

подключена к источнику питания. Если же на плавающем затворе выбранной ячейки памяти отрицательного электрического заряда нет (записан логический "0"), то этот транзистор тоже открыт, и на вход соответствующей периферийной схемы  действует низкий потенциал, который означает считывание "0".

действует низкий потенциал, который означает считывание "0".

Наличие двух систем ключевых транзисторов  и

и  обеспечивает возможность объединения многих матриц памяти в многомерную систему на кристалле с выделением отдельных субъединиц (блоков, страниц, банков) данных.

обеспечивает возможность объединения многих матриц памяти в многомерную систему на кристалле с выделением отдельных субъединиц (блоков, страниц, банков) данных.

Стирание информации здесь проводят обычно также со всей матрицы одновременно, но при этом записывают не "единицы", а "нули". Для этого все горизонтальные шины присоединяют к "земле", а на все вертикальные шины через периферийные электронные схемы  подают напряжение +5 В. При этом с плавающих затворов всех ячеек памяти стекает весь отрицательный электрический заряд.

подают напряжение +5 В. При этом с плавающих затворов всех ячеек памяти стекает весь отрицательный электрический заряд.

Для записи информации на выбранную горизонтальную шину подают импульс напряжения амплитудой +5 В, а на все другие горизонтальные шины подают потенциал, достаточный для открывания транзисторов независимо от имеющегося на их плавающем электроде заряда, но не достаточный для туннельного переноса электронов на плавающий электрод. А вертикальные шины тех разрядов, куда надо записать "1", соединяют с "землей". На другие вертикальные шины через периферийную электронную схему ПЭ подают потенциал +5 В, что делает невозможным перенос электрического заряда на плавающий электрод.

Сравнение вариантов флеш-памяти "NOR" и "NAND" и их применение

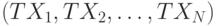

Матрицы флеш-памяти типа "NAND" оказались намного выгоднее с точки зрения топологии и себестоимости производства. Для сравнения на рис. 6.10 показаны поперечные сечения матриц памяти типа "NOR" (вверху) и "NAND" (внизу). Первое поперечное сечение выполнено вдоль горизонтальной шины (1), соединяющей управляющие затворы (4) всех транзисторов строки. Вертикальные шины, которые соединяют истоки (2) и которые соединяют стоки (3) всех транзисторов столбца, проходят перпендикулярно к плоскости сечения.

Рис. 6.10. Поперечное сечение пластины кремния с матрицами флеш-памяти типа "NOR" (вверху) и "NAND" (внизу): 1 – горизонтальная шина; 2 – вертикальная шина истоков; 3 – вертикальная шина стоков; 4 – управляющие затворы транзисторов

Поперечное сечение матрицы памяти типа "NAND" (внизу) выполнено вдоль столбца. Горизонтальные шины (1), которые образуют управляющие затворы всех транзисторов строки, здесь проходят перпендикулярно к плоскости сечения. Вертикальных шин вообще нет, так как их роль выполняют последовательно соединенные транзисторы ячеек памяти. Они максимально сближены как за счет того, что не нужны металлические выводы от истоков и стоков, так и за счет того, что один и тот же "карман"  -типа проводимости выполняет роль стока для одного транзистора и одновременно роль истока для соседнего. Все межсоединения выполнены здесь в один, а не в 2 яруса, как в матрицах типа "NOR".

-типа проводимости выполняет роль стока для одного транзистора и одновременно роль истока для соседнего. Все межсоединения выполнены здесь в один, а не в 2 яруса, как в матрицах типа "NOR".

В результате плотность размещения ячеек памяти в матрицах типа "NAND" в несколько раз выше, и поэтому себестоимость одного мегабайта памяти здесь в несколько раз меньше. Флеш-память типа "NAND" оказалась также значительно удобней для масштабирования, и сейчас ведущие фирмы мира изготовляют ее уже с проектно-технологическими нормами 22 нм и менее.

Благодаря высокому уровню интеграции, относительно малой себестоимости одного мегабайта памяти, малым размерам, высокому быстродействию и надежности наноэлектронная флеш-память вытесняет из употребления носители информации других типов. Отходят в прошлое гибкие магнитные диски и дисководы для них.

Весьма популярными стали флеш-брелки – легкие, компактные, элегантные, надежные карманные устройства памяти, с помощью которых можно просто и быстро переносить большие объемы информации с одного компьютера на другой. Уже выпускаются модели флеш-брелков с объемом памяти 1 Тб и даже больше и скоростью переноса данных от 1 до 100 Мбайт/с.

Широко используются наноэлектронные флеш-карты памяти, имеющие форму тонких прямоугольных пластин с контактами на периферии. Их широко используют во всех современных интеллектуальных мобильных устройствах: в цифровых фотоаппаратах и видеокамерах, в электронных книгах и учебниках, в сотовых телефонах, смартфонах и телевизорах, в мобильных медиаплеерах и устройствах для электронных игр, в навигаторах, и т.д. Их начинают все шире применять в новейших станках с числовым программным управлением и в новейшем автоматизированном промышленном оборудовании.

Развернулось серийное производство "твердотельных" аналогов жестких магнитных дисков (англ. solid-state drive, SSD). Кроме наноэлектронной флеш-памяти объемом до 1 Тб и более, в их состав входит наноэлектронный КМДП контролер, обеспечивающий возможность работы с операционными системами компьютеров и равномерное распределение запросов на перезапись информации по всему объему памяти. Ведь ресурс циклов перезаписи информации в флеш-памяти ограничен числом приблизительно 105. По этой причине и по показателю удельной себестоимости информации в стационарных компьютерах флеш-диски еще проигрывают конкуренцию жестким магнитным дискам. А вот в мобильных компьютерах и компьютерных системах (ноутбуки, нетбуки, коммуникаторы, мобильные аппараты для УЗ диагностики, и т.п.) флеш-диски уже начинают выигрывать – благодаря отсутствию в них подвижных частей и значительной стойкости к вибрациям и ударам, намного большему быстродействию и значительно меньшему энергопотреблению.

Флеш-память на МДП транзисторах с зарядовыми ловушками

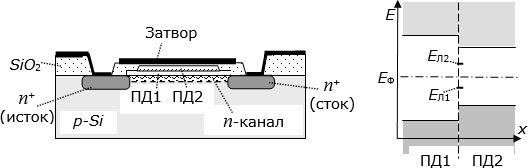

Свойства, подобные свойствам МДП транзисторов с плавающим затвором, имеют МДП транзисторы с зарядовыми ловушками. Структура такого транзистора показана на рис. 6.11 слева. Она подобна структуре п-канального МДП транзистора с плавающим затвором, изображенного на рис. 6.5, только вместо плавающего затвора тут сформирован второй слой подзатворного диэлектрика (ПД2), который отличается от первого слоя (ПД1).

Рис. 6.11. Слева – структура n-канального МДП транзистора с зарядовыми ловушками. Справа – энергетическая диаграмма перехода между двумя диэлектриками

На переходе между двумя слоями обычно возникают локальные дефекты с энергетическими уровнями ( и

и  ), расположенными глубоко под зоной проводимости. Соответствующая энергетическая диаграмма показана на

рис.

6.11 справа. Здесь вдоль вертикали отложена энергия, вдоль горизонтали – координата. Зоны проводимости выделены светло-серым, а валентные зоны – темно-серым цветом. Если энергетические уровни

), расположенными глубоко под зоной проводимости. Соответствующая энергетическая диаграмма показана на

рис.

6.11 справа. Здесь вдоль вертикали отложена энергия, вдоль горизонтали – координата. Зоны проводимости выделены светло-серым, а валентные зоны – темно-серым цветом. Если энергетические уровни  и

и  являются настолько глубокими, что тепловой энергии недостаточно для того, чтобы электрон мог самостоятельно перейти из этого энергетического уровня в зону проводимости, то такие локальные дефекты называют "электронными ловушками".

Попав на такие дефекты, электроны могут оставаться на них годами. И лишь под действием достаточно сильного электрического поля или ультрафиолетового облучения становятся возможными туннельные или оптические переходы электронов на такие ловушки и из них. Именно этим и объясняется способность транзисторов с электронными ловушками запоминать то или другое состояние: "0" – когда электронов в ловушках нет или "1" – когда электроны там есть.

являются настолько глубокими, что тепловой энергии недостаточно для того, чтобы электрон мог самостоятельно перейти из этого энергетического уровня в зону проводимости, то такие локальные дефекты называют "электронными ловушками".

Попав на такие дефекты, электроны могут оставаться на них годами. И лишь под действием достаточно сильного электрического поля или ультрафиолетового облучения становятся возможными туннельные или оптические переходы электронов на такие ловушки и из них. Именно этим и объясняется способность транзисторов с электронными ловушками запоминать то или другое состояние: "0" – когда электронов в ловушках нет или "1" – когда электроны там есть.

В диапазоне наноэлектронных размеров в качестве первого подзатворного диэлектрика (ПД1) часто используют окисел гафния толщиной в несколько нанометров, а в качестве второго (ПД2) – приблизительно такой же толщины слой нитрида кремния ( ). Разрабатывают также и 3-слойные системы, в которых слой диэлектрика с меньшей шириной запрещенной зоны энергий размещается между слоями диэлектриков с заметно большей шириной запрещенной зоны. Тогда весь промежуточный слой диэлектрика становится электронной ловушкой.

). Разрабатывают также и 3-слойные системы, в которых слой диэлектрика с меньшей шириной запрещенной зоны энергий размещается между слоями диэлектриков с заметно большей шириной запрещенной зоны. Тогда весь промежуточный слой диэлектрика становится электронной ловушкой.

На транзисторах с электронными ловушками также строят энергонезависимую флеш-память – с использованием тех же схем "NAND" и "NOR". В англоязычной литературе такую память называют "Charge Trap Flash" (CTF). Характеристики устройств такой памяти приблизительно такие же, как и у описанных выше типов флеш-памяти.