|

Здравствуйте Владимир (Ефименко). Я обучаюсь по программе повышения квалификации "Наноэлектронная элементная база информатики на основе полупроводников и ферромагнетиков". У меня проблема с тестом № 2 (к лекции № 2) по этой программе. Я несколько раз пытался пройти этот тест, но больше 50 баллов набрать не удаётся, хотя я всё делаю в соответствии сматериалом лекции. В заданиях этого теста есть ошибки, которые видны невооружённым глазом. Обращаюсь к Вам как к инспектору этой программы повышения квалификации. Найдите возможность исправить ошибки в тесте № 2. Из-за остановки на этом тесте я не могу двигаться дальше, а у меня очень ограниченное время на освоение этой программы. Заранее благодарен Вам за внимание к моим проблемам и помощь. |

Наноэлектронные устройства памяти на кремниевых КМДП транзисторах

"Динамическая" оперативная память с произвольным доступом

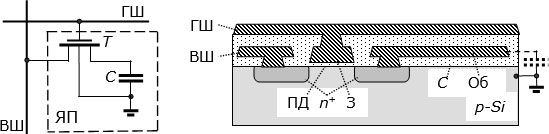

Наноэлектронные КМДП и МДП транзисторы используют и во многих других видах памяти. Одной из простейших и наиболее дешевых из них является так называемая "динамическая" оперативная память (англ. Dynamic Random Aaccess Memory, DRAM). На

рис.

6.3 слева показана принципиальная электрическая схема одной ячейки такой памяти (ЯП), обведенная штриховой линией, и способ ее подключения к горизонтальным (ГШ) и вертикальным (ВШ) шинам в матрице. Ключевой МДП транзистор может быть как  -канальным, так и

-канальным, так и  -канальным.

-канальным.

Справа показана конструкция такой ячейки для случая  -канального транзистора. Здесь в подложке из кремния р-типа проводимости сформированы карманы

-канального транзистора. Здесь в подложке из кремния р-типа проводимости сформированы карманы  -типа, между которыми возникает индуцированный канал проводимости. Над этим каналом сформированы подзатворный диэлектрик (ПД) и электрод затвора (З). В первом слое металлизации формируют систему вертикальных шин (ВШ), которые проходят перпендикулярно к плоскости сечения, и верхние обкладки (Об) конденсаторов (С), а во втором слое – систему горизонтальных шин (ГШ), которые проходят параллельно плоскости сечения. Уровни металлизации изолированы друг от друга и от пластины кремния слоями окисла. Роль нижней обкладки конденсаторов выполняет подложка из кремния

-типа, между которыми возникает индуцированный канал проводимости. Над этим каналом сформированы подзатворный диэлектрик (ПД) и электрод затвора (З). В первом слое металлизации формируют систему вертикальных шин (ВШ), которые проходят перпендикулярно к плоскости сечения, и верхние обкладки (Об) конденсаторов (С), а во втором слое – систему горизонтальных шин (ГШ), которые проходят параллельно плоскости сечения. Уровни металлизации изолированы друг от друга и от пластины кремния слоями окисла. Роль нижней обкладки конденсаторов выполняет подложка из кремния  -типа проводимости, которую соединяют с "землей".

-типа проводимости, которую соединяют с "землей".

Рис. 6.3. Слева – принципиальная электрическая схема, справа – структура ячейки динамической оперативной памяти

Как видим, ячейка динамической памяти очень проста – один  -канальный МДП транзистор (

-канальный МДП транзистор ( ) и один тонкопленочный конденсатор. При проектно-технологической норме 32 нм такая ячейка памяти занимает на пластине кремния площадь приблизительно

) и один тонкопленочный конденсатор. При проектно-технологической норме 32 нм такая ячейка памяти занимает на пластине кремния площадь приблизительно  , – на порядок меньше, чем ячейка описанной выше статической оперативной памяти. Поэтому и плотность хранения информации здесь на порядок выше, и себестоимость производства одного мегабита памяти на порядок меньше.

, – на порядок меньше, чем ячейка описанной выше статической оперативной памяти. Поэтому и плотность хранения информации здесь на порядок выше, и себестоимость производства одного мегабита памяти на порядок меньше.

Чтобы записать в ячейку памяти (ЯП) логическую "1", на соответствующие горизонтальную и вертикальную шину (ГШ и ВШ) подают положительное электрическое напряжение. Транзистор  открывается, и конденсатор

открывается, и конденсатор  заряжается. Чтобы записать логический "0", на горизонтальную шину (ГШ) подают положительное электрическое напряжение, а вертикальную шину (ВШ) соединяют с "землей". Через открытый транзистор

заряжается. Чтобы записать логический "0", на горизонтальную шину (ГШ) подают положительное электрическое напряжение, а вертикальную шину (ВШ) соединяют с "землей". Через открытый транзистор  конденсатор

конденсатор  быстро разряжается.

быстро разряжается.

В режиме считывания информации на горизонтальную шину (ГШ), которая является адресной, подают импульс положительного напряжения, и транзистор  открывается. Электрический заряд, накопленный на емкости

открывается. Электрический заряд, накопленный на емкости  , перераспределяется между ней и емкостью вертикальной шины. Поскольку матрицы динамической памяти всегда имеют большой объем и металлические шины намного длиннее размера ячейки, то электрическая емкость вертикальной шины обычно намного больше

, перераспределяется между ней и емкостью вертикальной шины. Поскольку матрицы динамической памяти всегда имеют большой объем и металлические шины намного длиннее размера ячейки, то электрическая емкость вертикальной шины обычно намного больше  . И поэтому изменение потенциала на вертикальной шине относительно невелико. Для того, чтобы считывание было надежным, перед считыванием паразитную емкость вертикальной шины заряжают до потенциала

. И поэтому изменение потенциала на вертикальной шине относительно невелико. Для того, чтобы считывание было надежным, перед считыванием паразитную емкость вертикальной шины заряжают до потенциала  , т.е. до половины напряжения питания

, т.е. до половины напряжения питания  .

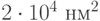

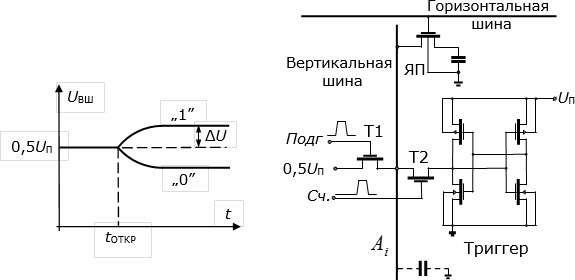

На

рис.

6.4 слева показано, как изменяется потенциал вертикальной шины после открывания транзистора соответствующей ячейки памяти. Если в ячейке памяти записана "1", то потенциал вертикальной шины несколько возрастает, а если записан "0", то – несколько убывает. В качестве дискриминатора и усилителя сигналов считывания на каждой вертикальной шине используют КМДП триггер (

рис.

6.4 справа).

.

На

рис.

6.4 слева показано, как изменяется потенциал вертикальной шины после открывания транзистора соответствующей ячейки памяти. Если в ячейке памяти записана "1", то потенциал вертикальной шины несколько возрастает, а если записан "0", то – несколько убывает. В качестве дискриминатора и усилителя сигналов считывания на каждой вертикальной шине используют КМДП триггер (

рис.

6.4 справа).

Рис. 6.4. Организация считывания данных в динамической оперативной памяти. Слева – изменение потенциала на вертикальной шине при считывании; справа – принципиальная электрическая схема узла формирования сигналов считывания, показана также одна из ячеек памяти (ЯП)

Узел формирования сигналов считывания работает так. Сначала по шине подготовки (Подг.) подают короткий импульс напряжения, под действием которого транзистор  открывается, и паразитная емкость вертикальной шины заряжается до потенциала

открывается, и паразитная емкость вертикальной шины заряжается до потенциала  . После этого на одну из горизонтальных шин, соответствующую заданному коду адреса, подают положительное напряжение, которое открывает транзисторы всех прилегающих к ней ячеек памяти (ЯП). В зависимости от заряда, который сохраняется на емкости ячейки, потенциал соответствующей вертикальной шины несколько возрастает или спадает. Дальше подается положительный импульс напряжения по шине считывания (Сч.), под действием которого открывается транзистор

. После этого на одну из горизонтальных шин, соответствующую заданному коду адреса, подают положительное напряжение, которое открывает транзисторы всех прилегающих к ней ячеек памяти (ЯП). В зависимости от заряда, который сохраняется на емкости ячейки, потенциал соответствующей вертикальной шины несколько возрастает или спадает. Дальше подается положительный импульс напряжения по шине считывания (Сч.), под действием которого открывается транзистор  .

Вертикальная шина электрически соединяется со входом триггера. Благодаря сильной обратной связи в триггере, уже небольшого отклонения потенциала вертикальной шины вверх или вниз от значения

.

Вертикальная шина электрически соединяется со входом триггера. Благодаря сильной обратной связи в триггере, уже небольшого отклонения потенциала вертикальной шины вверх или вниз от значения  достаточно для того, чтобы триггер перешел в соответствующее состояние ("1" или "0"). Паразитная емкость вертикальной шины и емкость соответствующей ячейки памяти (ЯП) при этом заряжаются через транзисторы триггера до полного высокого (близкого к

достаточно для того, чтобы триггер перешел в соответствующее состояние ("1" или "0"). Паразитная емкость вертикальной шины и емкость соответствующей ячейки памяти (ЯП) при этом заряжаются через транзисторы триггера до полного высокого (близкого к  ) или разряжаются до низкого потенциала, близкого к потенциалу "земли".

) или разряжаются до низкого потенциала, близкого к потенциалу "земли".

Недостатком ячеек динамической памяти является то, что электрический заряд на конденсаторах из-за наличия паразитных утечек постепенно уменьшается, и спустя некоторое время записанная информация может пропасть. Чтобы это не произошло, записанную информацию надо периодически обновлять. Поэтому такую память и называют "динамической". Процесс обновления информации называют регенерацией памяти.

Как видно из вышеописанного, в режиме считывания (а также записи) информация в соответствующих ячейках памяти регенерируется автоматически. Совсем другое дело в тех ячейках памяти, к которым нет обращения. Там записанную информацию надо автоматически обновлять с периодом регенерации, который составляет в разных вариантах исполнения динамической памяти от 1 до 64 мс. В диапазоне нанометровых размеров транзисторов чем меньше их размер, тем больше относительная роль паразитных токов утечки, и тем меньше должен быть период регенерации.

Режим регенерации подобен описанному выше режиму считывания, только информация не заносится в выходной регистр. Записанные в матрицу памяти данные регенерируются путем последовательной активации горизонтальных шин – одна за другой. Период регенерации отсчитывается специальными простыми таймерами. Часто применяют еще и температурный датчик. Благодаря этому при повышении температуры микросхемы памяти период регенерации автоматически сокращается, а при снижении – удлиняется. Это позволяет уменьшить потребление электроэнергии, затрачиваемой на регенерацию данных.

Чтобы регенерация не оказывала большого влияния на задержку исполнения внешних запросов к динамической памяти на считывание или на запись информации, изобретено много разных архитектурных и схемотехнических решений, которые реализованы в кристаллах памяти от разных производителей. Но главные решения присутствуют в кристаллах всех производителей, и на эти решения мы обратим ваше внимание.

В частности, весь большой массив ячеек памяти (а ныне это уже до сотни мегабайт на одном кристалле) разбивают на много отдельных матриц памяти ("банков", "страниц"), которые функционируют почти независимо одна от другой. Те матрицы, в которые занесена нужная информация, но к которым в текущий момент обращений нет, находятся в режиме оптимизированной автономной регенерации. А те, к которым идут обращения, регенерируются во время считывания/записи.

Наноэлектронная технология позволила применить и такую "роскошь", как создание на кристалле динамической памяти встроенных буферных блоков быстрой статической памяти. При появлении обращения к какой-либо из отдельных матриц памяти записанные в нее данные быстро копируются в один из буферных блоков статической памяти и дальше могут оперативно считываться или изменяться в ней. Практика показала, что следующие обращения к оперативной памяти примерно в 99 из 100 случаев адресуются к той же матрице и поэтому быстро обслуживаются буферным блоком статической памяти. В редких случаях обращения к другой матрице динамической памяти данные из нее быстро копируются во второй буферный блок статической памяти, а информация из предыдущего буферного блока параллельно перезаписываются в соответствующую матрицу динамической памяти. Удлинение времени реакции на относительно редкие запросы к другой матрице динамической памяти вполне компенсируется сверхбыстрым обслуживанием большинства других запросов.

Внутри кристаллов наноэлектронной динамической памяти для сокращения времени доступа и цикла считывания информации широко используют тактовые импульсы и параллельную обработку данных.

Дополнительные возможности оптимизации архитектуры динамической памяти появляются в системах обработки видеоизображений. Ведь там информация записывается и считывается по кадрам, т.е. заведомо определенными довольно большими блоками с заранее известной организацией их потоков. Учитывая это, в таких специализированных блоках наноэлектронной динамической памяти организуют эффективную, незаметную для пользователя, регенерацию данных и достигают высокой степени параллельности обработки данных внутри кристалла.

Тактовая частота современных наноэлектронных микросхем динамической памяти доведена уже до 3 ГГц, а длительность цикла получения данных из последовательно размещенных ячеек памяти – до значений порядка 1 нс.

Наноэлектронные микросхемы динамической памяти промышленно выпускаются огромными (многомиллионными) тиражами многими известными в мире корпорациями и, благодаря их относительно небольшой стоимости, широко применяются в компьютерах, цифровых видеокамерах, цифровых системах передачи изображений, звуков, и т.п. Каждый производитель динамической памяти в своих справочных материалах приводит информацию об особенностях своих микросхем, регламентацию порядка подачи и продолжительности информационных и управляющих сигналов, эксплуатационные данные.