|

Добрый день!

Скажите, пожалуйста,планируется ли продолжение курсов по нанотехнологиям? Спасибо, Евгений

|

Оценка производительности и живучести МКМД-БИТ-потокового предпроцессора системы астронавигации

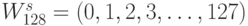

Первое значимое множимое является первым элементом вектор-столбца  построчной гистограммы и подается на 936(+2*128) такте. Первый значащий множитель

построчной гистограммы и подается на 936(+2*128) такте. Первый значащий множитель  подается на 934(+2*128) такте. На управляющий вход умножителя на

подается на 934(+2*128) такте. На управляющий вход умножителя на  такте подается циклическая константа

такте подается циклическая константа  , задающая цикл его работы. При этом следует помнить, что первые нулевые операнды множимого и множителя поступают на входы умножителя соответственно на 808 и 806 тактах.

, задающая цикл его работы. При этом следует помнить, что первые нулевые операнды множимого и множителя поступают на входы умножителя соответственно на 808 и 806 тактах.

Рис. 8.19. Топологическая схема модуля свертки вектор-столбца построчной гистограммы отфильтрованного изображения (SMM)

Циклическая константа  и поток весовых коэффициентов

и поток весовых коэффициентов  генерируются двумя взаимодействующими блоками управления WGU и CCU1(128), которые занимают на бит-матрице первые пять столбцов с 6-й по 24-ю строку.

генерируются двумя взаимодействующими блоками управления WGU и CCU1(128), которые занимают на бит-матрице первые пять столбцов с 6-й по 24-ю строку.

Блок генерации CCU1(128) циклической константы  выполнен по классической схеме делителя (на 24) частоты задающего генератора CG, содержащего циклическую константу

выполнен по классической схеме делителя (на 24) частоты задающего генератора CG, содержащего циклическую константу  (БП (23, 5)). В БП (20, 1) данная циклическая константа ветвится в двух направлениях, так как она используется и как независимая управляющая переменная, и как промежуточный аргумент, задающий величину и цикл приращения целочисленных значений

весовых коэффициентов

(БП (23, 5)). В БП (20, 1) данная циклическая константа ветвится в двух направлениях, так как она используется и как независимая управляющая переменная, и как промежуточный аргумент, задающий величину и цикл приращения целочисленных значений

весовых коэффициентов  в блоке WGU.

в блоке WGU.

Блок WGU имеет выход (6, 2, 2) с начальной задержкой 794 такта по отношению к обнуленному в DWHCU операнду и 922 такта по отношению к первому значащему операнду, имеющему в ML вес "единица". Для установки такой начальной задержки использована PD -ассоциативная схема записи однократной "единицы" в соответствующие разряды счетчика на Т -триггерах. Однократная "единица" формируется при включении субпроцессора БП с координатами (21, 3)-(21, 5) и распространяется вверх по 5-му столбцу бит-матрицы. Время начальной задержки фиксировано, но его можно изменить, модифицировав адреса разрядов счетчика, в которые попадает однократная "единица".

Блок обнуления ( DWHCU ) паразитных взаимодействий строк из разных кадров, попавших в одно 2-элементное "скользящее окно", генерирует циклическую константу вида: 32 "нуля" и

(214-32) "единиц". Он расположен на бит-матрице с координатами (10, 6)-(21, 9) и представляет собой два взаимодействующих счетчика, один из которых генерирует циклическую константу  (выход БП (13, 8, 2)), а второй -

(выход БП (13, 8, 2)), а второй -  (выход БП (12, 7, 2)). Циклическая константа

(выход БП (12, 7, 2)). Циклическая константа  используется как управляющая переменная в БП (7, 11), который реализует бит-инструкцию ST1, а вторая циклическая константа используется в этом же БП как информационная. Начальная задержка в блоке DWHCU устанавливается с помощью бит-инструкций AND и NAND в БП 6-го и 9-го столбцов. Само обнуление паразитных взаимодействий строк из разных кадров осуществляется в БП (6, 10), который реализует бит-инструкци

ю AND.

используется как управляющая переменная в БП (7, 11), который реализует бит-инструкцию ST1, а вторая циклическая константа используется в этом же БП как информационная. Начальная задержка в блоке DWHCU устанавливается с помощью бит-инструкций AND и NAND в БП 6-го и 9-го столбцов. Само обнуление паразитных взаимодействий строк из разных кадров осуществляется в БП (6, 10), который реализует бит-инструкци

ю AND.

Сумматор-накопитель ADDRV32 оператора свертки вектор-столбца построчной гистограммы обрабатываемого изображения выполнен по классической схеме с 32-битным аккумулятором (рис. 8.19-б - бит-матрица с координатами (6, 7)-(8, 10)).

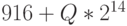

Строб "чтение" имеет вид: 32 "единицы" и (214-32) "нуля", предшествует полному циклу накопления, поступает на  такте на вход бит-процессора (7, 10, 1) и в инвертированном виде используется в БП (7, 9, 4) как строб сброса. Он генерируется блоком ( CADDR32 ), который занимает бит-матрицу с координатами (10, 10)-(13, 21). Задающий генератор этого блока размещен в БП (10, 12), который настроен на бит-инструкцию CG и генерирует циклическую константу

такте на вход бит-процессора (7, 10, 1) и в инвертированном виде используется в БП (7, 9, 4) как строб сброса. Он генерируется блоком ( CADDR32 ), который занимает бит-матрицу с координатами (10, 10)-(13, 21). Задающий генератор этого блока размещен в БП (10, 12), который настроен на бит-инструкцию CG и генерирует циклическую константу  , записанную со смещением на 7 тактов и потому имеющую шестнадцатеричное представление 10. Циклическая константа

, записанную со смещением на 7 тактов и потому имеющую шестнадцатеричное представление 10. Циклическая константа  формируется на выходе БП (15, 12, 2) и используется как управляющая переменная в БП (11, 11), настроенном на бит-инструкцию ST1. На нижний, информационный вход этого БП поступает циклическая константа

формируется на выходе БП (15, 12, 2) и используется как управляющая переменная в БП (11, 11), настроенном на бит-инструкцию ST1. На нижний, информационный вход этого БП поступает циклическая константа  . Установка начального состояния генер

атора строба CADDR32 осуществляется соответствующим размещением бит-инструкций AND и NAND в БП 10-го и 13-го столбцов бит-матрицы.

. Установка начального состояния генер

атора строба CADDR32 осуществляется соответствующим размещением бит-инструкций AND и NAND в БП 10-го и 13-го столбцов бит-матрицы.

Функциональный выход модуля свертки ADDRV32 построчной гистограммы расположен в бит-процессоре (7, 10, 4).

Накапливающий сумматор ADDRH32 определяет суммарную яркость каждого кадра обрабатываемого бинарного изображения, и он эквивалентен по функции сумматору ADDRV32 с той разницей, что в нем формируется прямая, а не взвешенная сумма элементов вектор-столбца

построчной гистограммы. Его информационный вход расположен в бит-процессоре (3, 10, 1), и начальная задержка на нем составляет 950 тактов по отношению к первому значащему операнду.

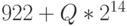

Управляющий вход этого сумматора расположен по адресу (3, 11, 4), на который на 918+Q*2^{14} такте поступает 32-битный "единичный" строб, который в бит-процессоре (2, 10) используется как сигнал "чтение", а в бит-процессоре (2, 11) - как сигнал "сброс".

Функциональный выход сумматора ADDRH32 расположен по адресу (2, 10, 4), на котором задержка составляет  такта. Топологический выход этого блока совпадает с входом операнда делителя, и на нем начальная задержка равна 966 тактов, которая учитывает сдвиг операнда на 7 бит влево, что соответствует умножению на нормирующий множитель 27. Такая нормировка обеспечивает условия правильного деления, когда частное должно быть меньше единицы.

такта. Топологический выход этого блока совпадает с входом операнда делителя, и на нем начальная задержка равна 966 тактов, которая учитывает сдвиг операнда на 7 бит влево, что соответствует умножению на нормирующий множитель 27. Такая нормировка обеспечивает условия правильного деления, когда частное должно быть меньше единицы.

Из приведенных данных видно, что в модуле свертки вектор-столбца ( SMM ) в одном 128-битном цикле выполняются:

- в 8-разрядном умножителе (ML): 1 операция умножения 16-битных операндов с 32-битным результатом, 1 операция задания разрядности и 1 пересылка произведения в сумматор-накопитель (пересылки множимого, множителя и управляющей константы учтены в предшествующих модулях);

- в блоке генерации весовых коэффициентов (WGU): 1 формирование, 1 чтение, 1 пересылка весового коэффициента;

- в блоке генерации циклической константы

(CCU1(128)): 16 операций генерации задающей циклической константы

(CCU1(128)): 16 операций генерации задающей циклической константы  и 32 ее пересылки; 4 операции контроля приращения циклической константы

и 32 ее пересылки; 4 операции контроля приращения циклической константы  и 36 ее пересылок, так как эта константа используется и как аргумент приращения при формировании весового коэффициента, и как сигнал "чтение" на каждом цикле работы модуля WGU, и как сигнал управления в модуле ML;

и 36 ее пересылок, так как эта константа используется и как аргумент приращения при формировании весового коэффициента, и как сигнал "чтение" на каждом цикле работы модуля WGU, и как сигнал управления в модуле ML; - в накапливающем сумматоре оператора свертки вектор-столбца (ADDRV32): 1 суммирование, 2 операции "И" и 3 пересылки;

- в блоке управления (CADDR32) циклом накопления: 16 генераций задающей циклической константы

и 32 ее пересылки; 4 генерации циклической константы

и 32 ее пересылки; 4 генерации циклической константы  и 4 ее пересылки; 4 контроля приращения циклической константы

и 4 ее пересылки; 4 контроля приращения циклической константы  и 4 ее пересылки; 4 контроля приращения циклической константы

и 4 ее пересылки; 4 контроля приращения циклической константы  и 8 ее пересылок в сумматор-накопитель;

и 8 ее пересылок в сумматор-накопитель; - в накапливающем сумматоре построчной гистограммы (ADDRH32): 1 суммирование, 2 операции "И" и 3 пересылки;

- в блоке обнуления (DWHCU) паразитных взаимодействий: 1 операция AND и 1 пересылка результата.

Таким образом, пропускная способность модуля свертки вектор-столбца ( SMM ) по потоку смеси из 8-битных, 32-битных и 128-битных слов-инструкций составляет: ![V_{I} = [(1+1+1)+(1+1+1)+16+32+4+36)]+(1+2+3)+ (16+32+4+4+4+4+4+8)+(1+2+3)+(1+1)]*F_{t} /128 = 184*F_{t} /128 = 1,4375*F_{t}](/sites/default/files/tex_cache/f8865e08f1be0537520a08a5cc021419.png) .

.

Модуль определения положение центра масс астроориентира на оси Х ( CMM - рис. 8.20) представляет собой:

- 8-разрядный делитель (DL), где в качестве делимого выступают значения

свертки вектор-столбца построчной гистограммы отфильтрованного изображения, а в качестве делителя - суммарная черно-белая яркость одного кадра обрабатываемого изображения;

свертки вектор-столбца построчной гистограммы отфильтрованного изображения, а в качестве делителя - суммарная черно-белая яркость одного кадра обрабатываемого изображения; - преобразователь "прямой код - дополнительный код" делимого (DCC) при смене знака с

на

на  , который объединен с блоком генерации циклической константы

, который объединен с блоком генерации циклической константы  .

.

Делитель DL (рис. 8.21) на 7 двоичных разрядов занимает бит-матрицу размером 8*62 БП и имеет:

- три информационных входа: делимого

(на рис. 8.21-а - это БП (3, 9, 3)) и делителя, который на 966 такте появляется на входах БП (4, 9, 3) и (6, 9, 3) с отрицательным

(на рис. 8.21-а - это БП (3, 9, 3)) и делителя, который на 966 такте появляется на входах БП (4, 9, 3) и (6, 9, 3) с отрицательным  и положительным

и положительным  знаком соответственно;

знаком соответственно; - один управляющий вход (1, 9, 3), где на 966 такте появляется циклическая константа

, задающая разрядность и формат обрабатываемых данных.

, задающая разрядность и формат обрабатываемых данных.

В данном случае использован классический для конвейерной арифметики формат фиксированной запятой: "нулевой" (старший) 32-й бит служит для блокирования паразитного распространения "единицы переноса" по потоку данных, 31-й бит - для хранения и передачи знака операнда, а остальные 30 бит - для хранения и передачи значащей части операндов.

Из приведенных данных видно, что из 214 тактов, соответствующих полному циклу обработки одного кадра изображения, делитель полезно используется только на 32 тактах, но занимает порядка 12 % всей площади бит-матрицы.

Первый результат на выходе делителя появляется начиная с 17699 такта, и представлен в инверсном виде.

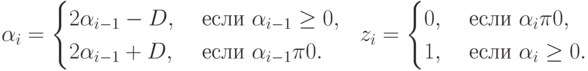

В делителе использован алгоритм деления со сдвигом и восстановлением остатка:

где  - остаток на

- остаток на  -м цикле деления;

-м цикле деления;  - разряд частного, причем

- разряд частного, причем  ,если речь идет о

,если речь идет о  , и

, и  , если речь идет о

, если речь идет о  . Здесь

. Здесь  - разрядность частного.

- разрядность частного.

Модуль преобразования из прямого в дополнительный код делителя  на рис. 8.21 занимает бит-матрицу в пределах БП (1, 10)-(6, 13). Его топология существенно "деформирована" по сравнению с рис. 4.2 (см. раздел 4.1), что связано с принудительной инверсией знакового разряда.

на рис. 8.21 занимает бит-матрицу в пределах БП (1, 10)-(6, 13). Его топология существенно "деформирована" по сравнению с рис. 4.2 (см. раздел 4.1), что связано с принудительной инверсией знакового разряда.

Из приведенных данных видно: в модуле определения положения центра масс астроориентира на оси Х ( CMM ) в одном 214 -битном цикле выполняются:

- в 7-разрядном делителе (DL): 29 операций деления 32-битных операнда с 7-битным результатом и 29 пересылок результата, из которых только один информативен;

- в преобразователе "прямой код - дополнительный код" делимого (DCC): 29 инверсий знака, 29 преобразований и 29 пересылок результата;

- в блоке генерации циклической константы

: 211 генераций циклической константы

: 211 генераций циклической константы  и 212 ее пересылок, 29 генерации циклической константы

и 212 ее пересылок, 29 генерации циклической константы  и 211 ее пересылок.

и 211 ее пересылок.

Таким образом, физическая пропускная способность модуля определения положения центра масс астроориентира на оси Х ( CMM ) по потоку 32-битных слов-инструкций составляет

![V_I = [(2^{9}+2^{9})+(2^{9}+2^{9}+2^{9})+(2^{11}+2^{12}+ 2^{9}+2^{11})]*F_t /2^{14} \approx 2^{13}*F_{t} /2^{14} = 0,5 F_{t}.](/sites/default/files/tex_cache/8a5648ba0da4317ce6e2b08aa7f8fd1c.png)

Фактическая (пользовательская) пропускная способность этого операционного модуля приближается к нулю, так как за 214 тактов фактически исполняется только одна 7-битная операция деления над 32-битными операндами.

Дублирующий канал арифметической обработки включает те же модули и блоки обработки, что и основной. Несмотря на то что основные и дублирующие каналы разнесены на топологической схеме, они сконструированы таким образом, чтобы все их входы и выходы были идентичными по временам начальной задержки, что обеспечивается выбором FIFO -регистровых коммутирующих каналов.