Процессоры архитектуры SPARC

Ядро SPARC

Каждое процессорное ядро содержит два целочисленных исполнительных блока, один блок с плавающей точкой, графический блок и блок криптографии. Потоки статически ассоциированы с каждым исполнительным модулем, до четырех потоков на целочисленный модуль.

Аппаратно SPARC-ядро поддерживает восемь потоков. Поддержка включает в себя полный регистровый файл (с восемью регистровыми окнами), включая большинство привилегированных регистров на каждый поток. Потоки разделяют между собой кэши инструкций и данных, блок вычислений с плавающей точкой (наличия одного блока с плавающей точкой вполне достаточно для многопоточных коммерческих приложений, в которых операции с плавающей точкой занимают порядка 1% от общего потока инструкций) [68, 69].

Каждое ядро имеет встроенный восьмиканальный кэш инструкций первого уровня размером 16 Кб, интегрированный с четырехканальным кэшем данных первого уровня. Кэш-память второго уровня составляет 4 Мб и разделяется всеми восемью ядрами процессора. Кэш второго уровня разделен на восемь банков, которые поддерживают восемь последовательных запросов к памяти для обеспечения высокой пропускной способности канала памяти. Пропускная способность подсистемы памяти при этом достигает 60 Гб/с.

Процессор Ultra SPARC T2 имеет также встроенный контроллер для шины PCIe и два 10 Гбит/с контроллера для сетей Ethernet.

Восемь процессорных ядер Niagara 2 связаны матричным переключателем с восемью банками 16-канального модульно-ассоциативного кэша второго уровня, общим объемом 4 Мбайт (у Niagara 1 — 3 Мбайт). Поскольку нагрузка на кэш в новом процессоре возросла вдвое, а объем кэша увеличился лишь на треть, для поддержания высокой производительности процессора разработчикам пришлось увеличить пропускную способность системы памяти. Вместо четырехканальной памяти DDR2, реализованной в Niagara 1, в процессоре используются четыре сдвоенных канала FBDIMM DRAM. Несколько большая по сравнению с DDR 2 энергоемкость новой подсистемы памяти с лихвой окупается приростом производительности — по оценкам разработчиков, в 1,7 раза.

UltraSPARC T2 также может быть сконфигурирован на работу в режимах четырех или двух банков кэша второго уровня (с размерами 1/2 и 1/4 общего размера кэша соответственно).

Процессор оборудован четырьмя контроллерами памяти и может работать с 64 банками памяти стандарта FB-DIMM. Каждый из котроллеров памяти обслуживает обращения к памяти от пары банков кэша второго уровня. В сокращенной конфигурации обращение к памяти может задействовать один из FBD-каналов (в нормальном режиме используются два канала). Каждое обращение к памяти выполняется независимо и может иметь независимый размер памяти и тип динамической памяти (DIMM). К примеру, различное количество ranks или различная длительность CAS-импульса. Программное обеспечение не должно занимать адресное пространство, более чем в четыре раза большее, чем наименьший объем в обращении кэша, поскольку линии кэша перекрываются вызовами кэша.

Частота DRAM-контроллера такая же, как и у DDR-шины, которая является удвоенной частотой DDR-памяти. FBDIMM-линии работают на частоте в шесть раз большей, чем DDR-шины [70-71-72].

Процессоры семейства Niagara считывают инструкции парами (четная и нечетная). При этом четная инструкция сразу же поступает в конвейер, а нечетная сохраняется в буфере до тех пор, пока не придет ее очередь (в каждый данный момент времени в конвейере находится одна инструкция). В ядре процессора Niagara 2 количество буферов инструкций увеличено до восьми (у каждого потока теперь свой буфер). В конвейере Niagara 2 появились дополнительные стадии. Конвейер целочисленных операций стал восьмистадийным, тогда как при выполнении инструкций, работающих с данными с плавающей запятой, конвейер насчитывает 12 стадий.

Некэшируемый (NCU) блок выполняет декодирование передач, адресованных в пространство ввода-вывода, и направляет их на соответствующие блоки (DMU, CCU). В дополнение к этому NCU работает основным (maintains) регистром статуса для внешних прерываний. Возможно также обнаружение коллизий прерываний, система почтовых ящиков, INTX, MSI, MSI-X.

Блок системного интерфейса (System Interface Unit (SIU)) соединяет DMU и кэш второго уровня. SIU — точка доступа для кэша L2 в сетевую подсистему. Интерфейс SIU-L2 Cache также является точкой захвата для доступа к шине PCI-Express.

UltraSPARC T2 имеет высокоскоростной последовательный интерфейс (50 Мб/с SSI), который соединяет его с программируемым массивом (FPGA), служащим для связи с загрузочным ПЗУ. Также SSI поддерживает режим простых линий ввода-вывода.

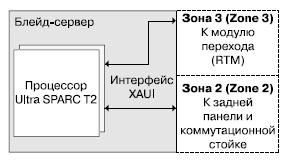

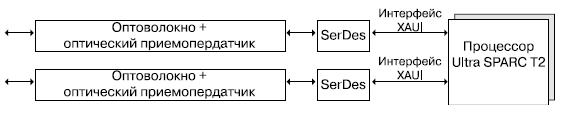

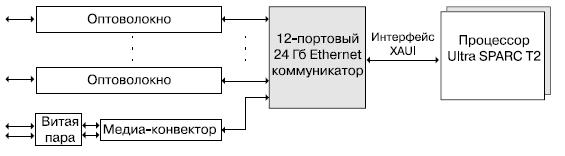

В дополнение процессор содержит два контроллера PCI Express, два 1/10 Гб/с Ethernet контроллера MAC-уровня с интерфейсами XAUI. Реализация PCIe включает поддержку спецификации 1.0а, поддерживаются конфигурационные режимы х1, х4, х8 при скорости данных 2,5Гб/с. Интерфейсы PCIe и XAUI могут быть запрограммированы для поддержки коротких и длинных связей, для работы и в блейд-приложениях, и в приложениях бэк-зоны.

Интерфейс PCIe оперирует на частоте 2,5 ГГц. Возможно управление уровнем сигнала для оптимизации передачи на короткие или длинные линии связи. Его реализация также включает поддержку транспортного уровня, уровня связи логического подуровня физического уровня.

Блок сетевых интерфейсов имеет две линии интерфейсов со скоростями 10 Гб/с, два XAUI-интерфейса, каждый из которых состоит из четырех полосного коммутатора CML, поддерживает дифференциальные сигналы в полосе 3,125 ГГц с программируемым уровнем сигнала. Каждый интерфейс имеет четыре приемо-передающие пары. Поддерживаются контрольные сигналы MDIO, аппаратное формирование и нумерация пакетов, классификация пакетов "на лету" на базе информации 1-4 уровней стека протоколов. Блок также имеет множественную поддержку прямого доступа в память и аппаратную поддержку виртуализации.

10-гигабитный Ethernet MAC (10GbE) поддерживает 16 MAC-адресов на порт, поддержку кадров длиной до 9216 байт, поддержку пауз между кадрами по стандарту IEEE 802.3. Возможна настройка времени паузы. Поддерживаются сброс пакетов, содержащих ошибки, проверка ошибок пакетов, вычисление и проверка контрольной суммы, сброс пакетов с ошибкой контрольной суммы.

Примеры применения процессоров Ultra Sparc T2 представлены на рис. 12.3- рис. 12.6.

Рис. 12.3. Серверы приложений, системы обнаружения вторжений, криптография, контроллеры беспроводных сетей — 10 Гб/с решение

Рис. 12.4. Серверы приложений, системы обнаружения вторжений, криптография, контроллеры беспроводных сетей — 12/24 Гб/с решение

Номинальное энергопотребление процессора составляет 95 Вт, максимальное — 123 Вт. Спектр возможных конфигураций количества ядер процессора, тактовых частот и потребляемой мощности представлены в таблице 12.2.

| Число ядер | Частота (ГГц) | Потребляемая мощность (Вт) |

|---|---|---|

| 8 | 1,2 | 91 |

| 8 | 0,9 | 65 |

| 6 | 0,9 | 57 |

| 4 | 0,9 | 46 |

По данным Sun, производительность при выполнении отдельного потока (при полной загрузке многопоточной системы процессора), содержащего целочисленные инструкции, должна возрасти на 40%. Учитывая незначительный прирост тактовой частоты, а также тот факт, что большее количество потоков потребует более сложного механизма переключения, 40-процентный прирост производительности следует отнести на счет различных микроархитектурных улучшений. В то же время производительность приложений, нуждающихся в большом количестве вычислений с плавающей запятой, возрастет на порядок. В отношении энергопотребления показатели Niagara 2 выглядят не менее впечатляюще. По словам одного из разработчиков, Грега Грохоцки, Niagara 2 обеспечивает вдвое большую производительность на каждый затраченный ватт по сравнению с предыдущей моделью. В целом процессор Niagara 2 можно рассматривать как удачную основу для построения недорогих серверов, в которых способность обрабатывать много потоков одновременно важнее высокой скорости выполнения каждого отдельного потока.

Краткие итоги

Процессор UltraSPARC T2 представляет собой высокоинтегрированную многоядерную и многопоточную систему на кристалле. Процессоры содержат от четырех до восьми независимых 64-разрядных SPARC-ядер, каждое из которых имеет аппаратную поддержку выполнения восьми независимых потоков. Каждое из ядер имеет два целочисленных исполнительных блока, математический сорпоцессор, криптографический сопроцессор. Имеет интегрированные контроллеры памяти, системной шины PCIe, Ethernet-контроллеры.

Основная область применений — серверы приложений, веб-серверы.

Контрольные вопросы

- Опишите структуру процессоров UltraSPARC T2.

- Как организована многопоточность в архитектуре SPARC?

- Укажите типовые схемы применения процессоров SPARC.

- Как организована кэш-память в UltraSPARC T2?

Упражнения

- Проследите динамику развития процессоров архитектуры SPARC по следующим показателям — количество транзисторов, технологический процесс, пиковая производительность, потребляемая мощность, количество аппаратно поддерживаемых потоков на одно ядро, количество ядер.

- Сравните относительные показатели производительности процессоров SPARC в разрезах: пиковая производительность/потребляемая мощность и технологический процесс/потребляемая мощность. Дайте характеристику полученным зависимостям.