Лекция 3: Высокопроизводительные многоядерные процессоры для встраиваемых приложений

Семейство процессоров Tile-Gx

Компания Tilera 26 октября 2009 года анонсировала стоядерные 64bit RISC-процессоры серии Tile-Gx общего назначения для применения в серверах, выполняющих многопоточные приложения. Процессор выполнен по 40-нанометровому технологическому процессу с максимальным тепловыделением 55 ватт (16-ядерный вариант — около 5 ватт). За счет применения специализированных модулей процессор сможет обеспечивать поток до 40 Гбит/с шифрованного трафика и до 20 Гбит/с сжатого в режиме full duplex. Процессор изначально разрабатывается для работы под операционной системой Linux. Также представлены чипы с 64, 36 и 16 ядрами ( таблица 3.1).

Процессоры несовместимы напрямую с чипами на базе микроархитектуры x86, однако поддерживают ОС на базе ядра Linux. Для того чтобы использовать привычные приложения, их необходимо сортировать с помощью прилагаемых программных инструментов (совместимость на уровне исходных текстов).

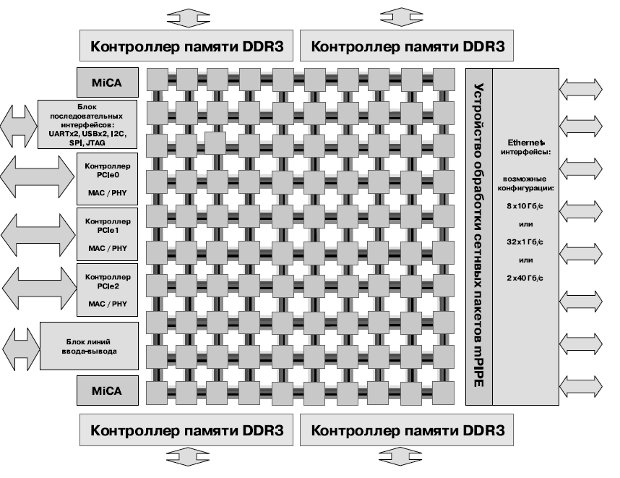

Семейство Tile-Gx [10] выводит вычисления с использованием 64-

разрядных процессоров на новый уровень, позволяя многим приложениям достигать высоких показателей производительности. Семейство включает в себя устройства с количеством ядер от 16-ти до 100 (

рис.

3.9), соединенных накристальной сетью Tilera's iMesh  .

.

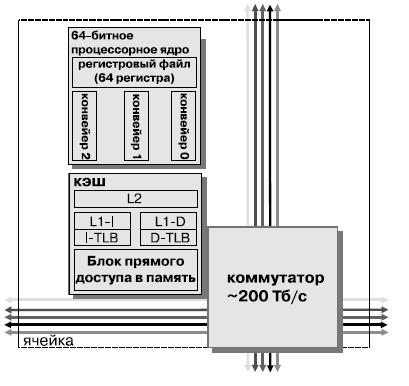

Так же, как и в предыдущих семействах, составной единицей процессора является ячейка, содержащая полноценный процессор с кэшами первого и второго уровней и неблокируемый коммутатор, соединяющий процессор (вычислительное ядро) с сетью ( рис. 3.10). Ядра, как и в предыдущих процессорах данной компании, могут работать как под управлением отдельной операционной системы, так и сгруппированными для работы под многопроцессорной системой типа SMP Linux.

Процессоры семейства Tile-Gx снижают стоимость разработки системы благодаря наличию контроллеров памяти и ввода-вывода, уменьшая тем самым количество внешних компонент.

Технология TileDirect позволяет осуществлять согласованный ввод-вывод непосредственно в кэш ячейки процессора, что существенно снижает задержки при обработке пакетов информации. Система распределенного когерентного кэша Tilera's DDC  (Dynamic Distributed Cache)

увеличивает производительность многопоточных приложений и приложений, использующих разделяемую память. Ячейки могут быть сгруппированы в независимые вычислительные кластеры, выполняющие каждый

свое приложение.

(Dynamic Distributed Cache)

увеличивает производительность многопоточных приложений и приложений, использующих разделяемую память. Ячейки могут быть сгруппированы в независимые вычислительные кластеры, выполняющие каждый

свое приложение.

Процессоры программируются при помощи языков С, С++, что позволяет разработчикам переносить на них существующие приложения.

Вычислительное ядро представляет собой 64-разрядный VLIW-процессор с длиной команд 64 бита, содержащий 64 регистра в регистровом файле, трехуровневый конвейер с возможностью выполнения до 3 команд за цикл, кэши первого уровня для данных и инструкций размерами по 32 Кб и 256 Кб кэша второго уровня. Тактовые частоты лежат в пределах 1-1,5 ГГц.

Кэш третьего уровня образуется при объединении кэшей отдельных

ячеек — Tilera's DDC  (суммарный размер кэша для стоядерного процессора составляет при этом 32 Мб).

(суммарный размер кэша для стоядерного процессора составляет при этом 32 Мб).

Скорость передачи данных между ядрами на кристалле составляет порядка 200 Тбит/с. Наличие четырех контроллеров памяти (DDR3) обеспечивает суммарную пропускную способность обмена с памятью 500 Гбит/с. Процессор может иметь до восьми десятигигабитных Ethenet-интерфейсов (XAUI), до трех интерфейсов PCIe второго поколения, до 32-х гигабитных Ethernet-интерфейсов (МАС), устройство обработки сетевых пакетов mPIPE, устройства шифрования и сжатия данных.

Все это позволяет процессору работать с сетевыми приложениями с уровнем трафика 40-80 Гб/с (пропускная способность при обработке пакетов 80 Гб/с, при обработке VPN трафика 40 Гб/с), обеспечивает пропускную способность по PCIe до 80 Гб/с.

Суммарное энергопотребление лежит в пределах 10-50 ватт.

Основные области применения:

- сетевые приложения — межсетевые экраны, VPN, мониторинг трафика и сети;

- инфраструктура систем беспроводной связи — контроллеры базовых станций, шлюзы, мультимедийные шлюзы;

- мультимедийные приложения — обработка видеоданных, IPTV;

- "облачные" вычисления — веб-приложения, базы данных, хранилища данных.

Процессор CSX700

Архитектура процессора CSX700 была разработана для решения проблемы размеров, веса и потребляемой мощности (Size, Weight and Power (SWAP)), которая, как правило, доминирует во встраиваемых высокопроизводительных приложениях. Путем интегрирования процессоров, системных интерфейсов и встроенной памяти с коррекцией ошибок, CSX700 представляет собой экономичное, надежное и производительное решение, отвечающее требованиям современных приложений [13-14-15].

Процессор представляет собой архитектуру с массовым параллелизмом данных и высокой степенью эффективности и надежности. Архитектура нацелена на интеллектуальную обработку сигналов и обработку изображений во временной и частотной областях.

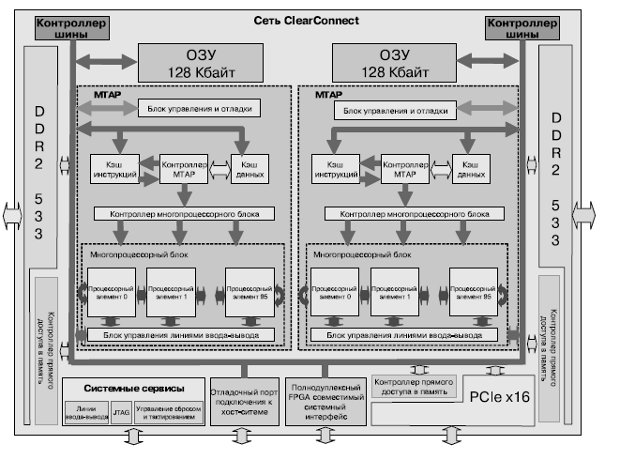

Кристалл CSX700 содержит 192 высокопроизводительных процессорных ядра, встроенную буферную память размером 256 Кбайт (два банка по 128 Кбайт), кэш данных и кэш команд, ECC защиту внутренней и внешней памяти, встроенный контроллер прямого доступа в память. Для обеспечения накристальной и межкристальной сети используется технология ClearConnect NoC ( рис. 3.11).

Интерфейс внешней памяти имеет 72 бита для контроля и коррекции данных (Error Checking and Correction — ECC). Используется память 64-бит DDR2 SDRAM объемом до 4 Гбайт. Процессор имеет 64- разрядное адресное пространство, которое отображается в 48-разрядное физическое. Порты CCBR0 и CCBR1 предназначены для образования мультикристальных систем, а также могут служить для подключения ПЛИС.

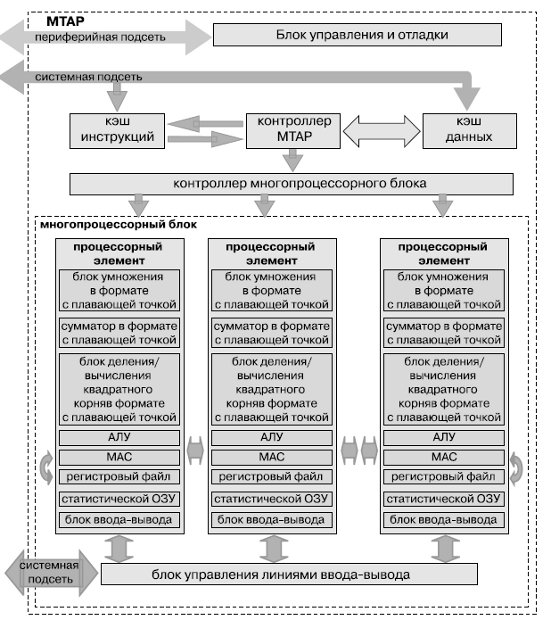

Процессор состоит из двух относительно независимых модулей (ядер) MTAP, содержащих кэши инструкций, данных, блоки управления процессорными элементами, и набор из 96 вычислительных ядер — процессорных элементов (PE) ( рис. 3.12) [15]. Поддерживает одновременное выполнение восьми потоков.

На каждом такте процессор извлекает команду, декодирует ее и направляет в исполнительные блоки mono или poly либо на контроллер ввода-вывода. Набор команд традиционен для RISC-процессоров — это трехадресные команды. Кроме того, процессор выполняет команды перехода и управляет переключением потоков. Команды выполняются над операндами mono или poly, причем некоторые из них реализуются только в каком-то одном блоке (например, команды переходов — лишь в mono)[14].

Каждое ядро имеет двойной блок вычислений с плавающей точкой (сложение, умножение, деление, вычисление квадратного корня, поддерживаются числа одинарной и двойной точности), 6 Кбайт высокопроизводительной оперативной памяти, 128-байтный регистровый файл. Поддерживается 64-битное виртуальное адресное пространство и 48-битное реальное.

Технические характеристики процессора:

- тактовая частота ядер — 250 МГц;

- 96 ГФлоп двойной или одинарной точности;

- поддерживает 75 ГФлопс двойной DGEMM;

- производительность целочисленных операций — 48 ГMAC/с (умножений с накоплением в секунду);

- рассеиваемая мощность — 9 Вт;

- пропускная способность внутренних шин памяти — 192 Гбайт/с;

- две внешних шины памяти — 4 Гбайт/с;

- скорость обмена данными между отдельными процессорами — 4 Гбайт/с;

- интерфейсы PCIe, 2х DDR2 DRAM (64 бита).

Внутрикристальная магистраль позволяет одновременно выполнять несколько обменов, например, обеспечивает доступ процессора к внутренней памяти. Кроме того, она дает возможность вести передачу данных из внешней памяти на порты CCBR0 или CCBR1 с использованием канала DMA.

Ядра синхронно исполняют один поток команд в режиме SIMD. Данные, которые должны обрабатываться параллельно, снабжены описателем poly.

Процессор поддерживает для каждого потока его контекст. Если PE- ядра выполняют длительный ввод-вывод, то процессор должен переключиться на другой поток. При этом потоки имеют приоритеты, и готовый поток с более высоким приоритетом прерывает выполнение потока с более низким. Потоки синхронизируются друг с другом и контроллерами ввода-вывода через аппаратные семафоры.

Семафоры представляют собой специальные регистры, значения которых увеличиваются или уменьшаются с помощью неделимых атомарных команд — соответственно, signal и wait. Если wait выполняется над семафором с нулевым значением, то выполнение команды приостанавливается до тех пор, пока не будет исполнена команда signal над этим семафором в другом треде или устройстве. Операции над семафорами способны выполнять и аппаратные блоки, например, контроллеры ввода-вывода.

Каждое ядро PE может выполнять или не выполнять команды в зависимости от значения разрешающих битов. Если все эти биты составляют "1", то команда выполняется. Если же хотя бы один из таких битов равен "0", большинство команд не выполняются (за исключением, например, команд изменения состояния разрешающих битов). Регистр разрешающих битов трактуется как стек: биты заходят в него через вершину.

Условное выполнение команд в PE поддерживается poly-командами перехода: if, else, endif и др. Они управляют значениями битов разрешения. Например, при выполнении команды if сравнения двух операндов во всех PE происходит следующее: в тех PE, где есть совпадение, в вершину стека будет помещена "1", а в тех, где обнаружено несовпадение, в вершину стека помещается "0". Соответственно, эти PE будут или не будут выполнять последующие команды — вплоть до команды endif, которая "вытолкнет" из стека значение, занесенное командой if. Стек имеет фиксированный размер, поэтому необходимо следить за его переполнением.

Команды чтения и записи из локальной памяти PE в регистры также могут выполняться или нет в зависимости от значения разрешающего бита. Для безусловного выполнения обмена между памятью и регистрами введены специальные команды forced load и forced store.

Канал ввода-вывода PE включает в себя контроллер и один или несколько каналов прямого доступа. Контроллер интерпретирует команды ввода-вывода и взаимодействует с тредами посредством семафоров. Обмен между локальной памятью PE и внешними устройствами выполняется путем программируемого ввода-вывода или с использованием каналов прямого доступа в локальную память. Каждый процессор может читать свою часть данных или выполнять общее чтение — с "нарезкой" одинаковых блоков для каждого процессора.

Процессорные элементы (PE) способны осуществлять обмен с "соседями" справа и слева. На каждом такте PE может выполнить передачу из своего регистра в регистр правого или левого "соседа" и получить одновременно справа и слева данные в свои регистры. Используются команды сдвига вправо и влево, а также передачи "соседу". Если PE имеет бит разрешения "0", то соседний процессор не может изменить состояние его регистров.

Разработанный для низкопотребляющих систем, данный процессор сочетает управление тактовой частотой, обычное для встраиваемых систем, с относительно низкой тактовой частотой. Управление частотой позволяет регулировать производительность приложений при работе в условиях определенного энергопотребления и теплового окружения.

CSX700 поддерживается профессиональной средой разработки (SDK) на основе технологии Eclipse с визуальными средствами отладки приложений, базирующейся на оптимизированном компиляторе ANSI C с расширениями для параллельного программирования. В дополнение к стандартной библиотеке С идет набор оптимизированных библиотек с такими функциями, как БПФ, BLAS, LAPACK и др.

Краткие итоги

Представленные в лекции процессоры фактически демонстрируют два подхода к построению процессоров с большим количеством ядер: MIMD — архитектура с развитой сетью обмена данными и SIMD — с обработкой однотипных данных в несколько потоков.

Основной структурной единицей процессоров Tile является ячейка (плитка), содержащая процессорный элемент и коммутатор.

Для устранения узкого места при доступе к внешней памяти используется двухуровневое построение кэша, в дополнение к этому ядра имеют доступ к кэшу второго уровня других ядер — так называемый распределенный кэш третьего уровня.

Основные целевые области применения процессоров Tile — сетевая инфраструктура, сервис-ориентированные приложения, "облачные" вычисления, обработка мультимедийных данных.

Структурной единицей процессора CSX700 можно назвать многопотоковый процессорный массив — MTAP.

Целевое назначение этого процессора — обрабока сигналов и изображений.

Оба процессора имеют среды разработки и отладки приложений на базе Eclipse, основной язык программирования — С, прилагаются также наборы библиотек и тестовых приложений.

На базе своих процессоров фирмы предлагают как независимые вычислительные модули, так и платы расширения с интерфейсом PCIe.

Контрольные вопросы

- Архитектура процессоров Tile — основные принципы построения, общие черты.

- Опишите топологию связей между ядрами в процессорах Tile. В чем состоят ее преимущества?

- Как организована подсистема памяти процессоров Tile?

- Опишите общую структуру процессора CSX700.

- Каким образом реализована поддержка многопоточности в процессоре CSX700?

Упражнения

- Сравните типовые характеристики задач для процессоров Tilera и ClearSpeed.

- Оцените эффекивность передачи данных между процессорами в процессорах Tilera и ClearSpeed.