Подключение периферийных устройств и расширение системы

Если рассмотреть популярные варианты компоновки систем с аппаратными или программными процессорными ядрами, то можно увидеть примерно следующее.

Популярным решением во многих IDE различных производителей FPGA является шина AXI - так, например, в Vivado достаточно много IP-ядер завязанных на AXI.

Многие технические решения, особенно по замещению процессорных ядер уже в микроконтроллерных решениях является шина AHB - конечно, не в рамках FPGA, но в микроконтроллерах китайского производства часто можно встретить микроконтроллеры-дубли, в которых ARM ядро замещено ядром RISC-V или вообще есть возможность выбора при включении, какое из ядер будет активно.

Рассмотренный ранее софт-процессор SCR1 также для взаимодействия с внешними устройствами использует в зависимости от конфигурации или шину AXI, или AHB/

В Open-Source проектах и их экосистеме популярны IP-ядра для шины Wishbone.

Ниже попробуем кратко рассмотреть особенности каждой из упомянутых шин.

AXI

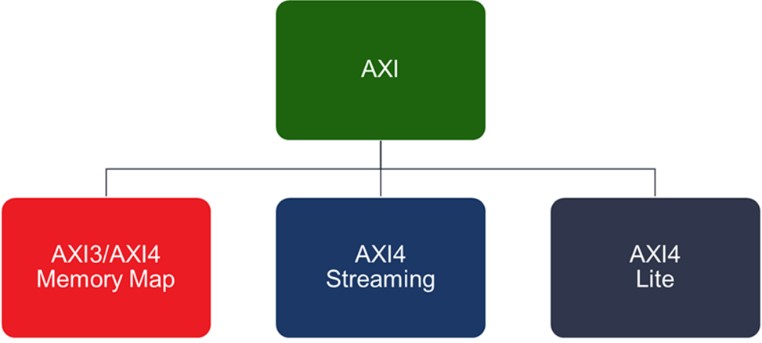

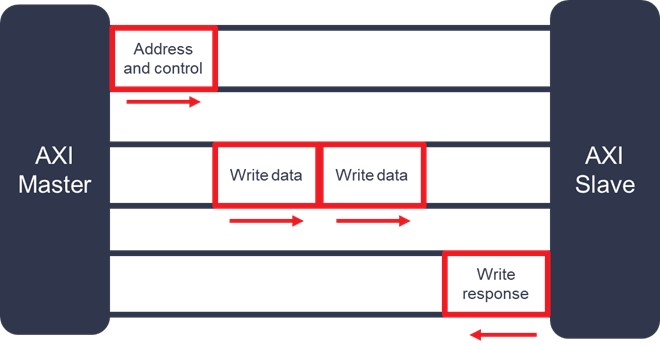

AXI (Advanced eXtensible Interface) - продвинутый это протокол интерфейса, определенный ARM как часть стандарта AMBA (Advanced Microcontroller Bus Architecture) - рис.11.1.

Протокол AXI4 был разработан для приложений с высокой пропускной способностью и низкой задержкой. Он предназначен для обеспечения связи между ведущим и ведомыми устройствами. Главным устройством обычно является DMA или центральный процессор, а подчиненными - контроллеры DRAM или контроллеры других специальных протоколов: UART, SPI и другие. Иногда один компонент может реализовывать несколько экземпляров этого протокола. Обычно префикс используется для различения нескольких интерфейсов AXI4.

Существует 3 типа AXI4-интерфейсов (AMBA 4.0):

- AXI4 (Полный AXI4): для высокоскоростных устройств, как правило отображаемых в память процессорной системы (memory-mapped);

- AXI4-Lite: для простой передачи данных с использованием памяти с низкой пропускной способностью (например, в регистры управления и состояния и из них);

- AXI4-Stream: для высокоскоростной потоковой передачи данных.

Каналы AXI

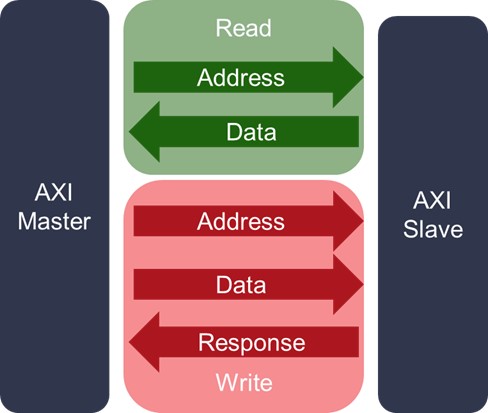

Протокол AXI определяет 5 каналов, два используются для транзакций чтения;

- адреса чтения;

- данных.

Три канала используются для транзакций:

- записи;

- адреса записи, данных;

- ответа на запись.

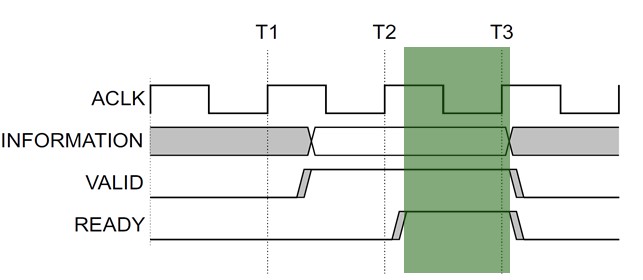

Канал - это независимая совокупность сигналов AXI, связанных с сигналами VALID и READY.

Фрагмент данных, передаваемый по одному каналу, называется передачей. Передача происходит, когда как VALID, так и READY сигнал находятся на высоком уровне, при фронте тактового сигнала Например, на рисунке 11.3 ниже передача выполняется на такте T3.

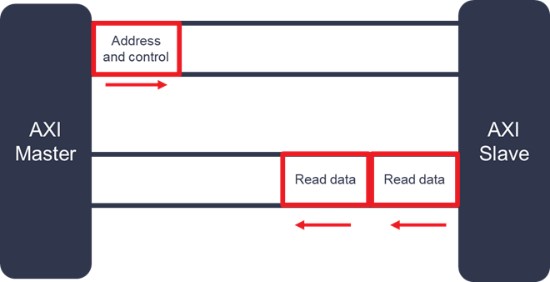

Транзакции чтения AXI требуют многократного обмена сигналами по двум каналам чтения. Сначала на канал считывания адреса передается от ведущего устройства к ведомому для установки адреса и некоторых управляющих сигналов. Затем данные для этого адреса передаются от ведомого устройства к ведущему устройству по каналу считывания данных. Обратите внимание, на рис. 4 при чтении одного адреса может быть передано несколько данных. Этот тип транзакции называется пакетной (brust).

Транзакции записи AXI также требуют многократной передачи данных по трем каналам считывания. Сначала канал записи адреса передается ведущим на ведомое устройство для установки адреса и некоторых управляющих сигналов. Затем данные для этого адреса передаются ведущим на ведомое устройство по каналу записи данных. Наконец, ответ на запись отправляется от ведомого устройства к ведущему по каналу ответа на запись, чтобы указать, была ли передача успешной.