Процессоры Intel

Хронология процессоров Intel

64-битные процессоры: EM64T — Микроархитектура Intel Core Xeon

Woodcrest — 65-нм технологический процесс.

Микропроцессор для серверов и рабочих станций с поддержкой симметричной многопроцессорности (SMP) (в случае двухпроцессорных систем).

Представлен 26 июня 2006 года.

Двухъядерный Dual-Core микропроцессор.

Поддержка инструкций SIMD: SSE4.

Реализованы технологии:

- Intel Virtualization Technology — поддержка нескольких операционных систем на одном компьютере;

- EIST (Enhanced Intel SpeedStep Technology) в моделях 5140, 5148LV, 5150, 5160;

- Execute Disable Bit;

- LaGrande Technology — enhanced security hardware extensions;

- iAMT2 (Intel Active Management Technology) — удаленное управление компьютерами.

Варианты:

- Xeon 5160 — 3,00 ГГц (4 Мб L2, 1333 МГц FSB, 80 Вт);

- Xeon 5150 — 2,66 ГГц (4 Мб L2, 1333 МГц FSB, 65 Вт);

- Xeon 5140 — 2,33 ГГц (4 Мб L2, 1333 МГц FSB, 65 Вт);

- Xeon 5130 — 2,00 ГГц (4 Мб L2, 1333 МГц FSB, 65 Вт);

- Xeon 5120 — 1,86 ГГц (4 Мб L2, 1066 МГц FSB, 65 Вт);

- Xeon 5110 — 1,60 ГГц (4 Мб L2, 1066 МГц FSB, 65 Вт);

- Xeon 5148LV — 2,33 ГГц (4 Мб L2, 1333 МГц FSB, 40 Вт) — Low Voltage Edition.

Clovertown — 65-нм технологический процесс.

Микропроцессор для серверов и рабочих станций с поддержкой симметричной многопроцессорности (SMP) (в случае двухпроцессорных систем).

Представлен 13 декабря 2006 года.

Четырехъядерный Quad-Core микропроцессор.

Реализованы технологии:

- Intel Virtualization Technology — поддержка нескольких операционных систем на одном компьютере;

- EIST (Enhanced Intel SpeedStep Technology);

- Execute Disable Bit;

- LaGrande Technology — enhanced security hardware extensions;

- SSSE3 SIMD instructions;

- iAMT2 (Intel Active Management Technology) — удаленное управление компьютерами.

Варианты:

- Xeon X5355 — 2,66 ГГц (2x4 Мб L2, 1333 МГц FSB, 105 Вт);

- Xeon E5345 — 2,33 ГГц (2x4 Мб L2, 1333 МГц FSB, 80 Вт);

- Xeon E5335 — 2,00 ГГц (2x4 Мб L2, 1333 МГц FSB, 80 Вт);

- Xeon E5320 — 1,86 ГГц (2x4 Мб L2, 1066 МГц FSB, 65 Вт);

- Xeon E5310 — 1,60 ГГц (2x4 Мб L2, 1066 МГц FSB, 65 Вт);

- Xeon L5320 — 1,86 ГГц (2x4 Мб L2, 1066 МГц FSB, 40 Вт) — Low Voltage Edition.

Intel Core 2

Conroe — 65-нм технологический процесс.

Микропроцессор для настольных систем.

Представлен 27 июля 2006 года.

Поддержка инструкций SIMD: SSE3.

Количество транзисторов: 291 миллион у моделей с 4 Мб кэш-памяти.

Реализованы технологии:

- Intel Virtualization Technology — аппаратная виртуализация;

- LaGrande Technology — аппаратная технология защиты информации;

- Execute Disable Bit;

- EIST (Enhanced Intel Speed Step Technology);

- iAMT2 (Intel Active Management Technology) — удаленное управление компьютерами.

Варианты:

- Core 2 Duo E6850 — 3,00 ГГц (4 Мб L2, 1333 МГц FSB);

- Core 2 Duo E6800 — 2,93 ГГц (4 Мб L2, 1066 МГц FSB);

- Core 2 Duo E6750 — 2,67 ГГц (4 Мб L2, 1333 МГц FSB);

- Core 2 Duo E6700 — 2,67 ГГц (4 Мб L2, 1066 МГц FSB);

- Core 2 Duo E6600 — 2,40 ГГц (4 Мб L2, 1066 МГц FSB);

- Core 2 Duo E6550 — 2,33 ГГц (4 Мб L2, 1333 МГц FSB);

- Core 2 Duo E6420 — 2,13 ГГц (4 Мб L2, 1066 МГц FSB);

- Core 2 Duo E6400 — 2,13 ГГц (2 Мб L2, 1066 МГц FSB);

- Core 2 Duo E6320 — 1,86 ГГц (4 Мб L2, 1066 МГц FSB);

- Core 2 Duo E6300 — 1,86 ГГц (2 Мб L2, 1066 МГц FSB).

Allendale — 65-нм технологический процесс.

Микропроцессор для настольных систем.

Представлен 21 января 2007 года.

Поддержка инструкций SIMD: SSE3.

Количество транзисторов: 167 миллионов.

Реализованы технологии:

- LaGrande Technology — аппаратная технология защиты информации;

- Execute Disable Bit;

- EIST (Enhanced Intel Speed Step Technology);

- iAMT2 (Intel Active Management Technology) — удаленное управление компьютерами.

Варианты:

- Core 2 Duo E4700 — 2,60 ГГц (2 Мб L2, 800 МГц FSB, нет VT);

- Core 2 Duo E4600 — 2,40 ГГц (2 Мб L2, 800 МГц FSB, нет VT);

- Core 2 Duo E4500 — 2,20 ГГц (2 Мб L2, 800 МГц FSB, нет VT);

- Core 2 Duo E4400 — 2,00 ГГц (2 Мб L2, 800 МГц FSB, нет VT);

- Core 2 Duo E4300 — 1,80 ГГц (2 Мб L2, 800 МГц FSB, нет VT);

- Core 2 Duo E4200 — 1,60 ГГц (2 Мб L2, 800 МГц FSB, нет VT).

Conroe XE — 65-нм технологический процесс.

Микропроцессор для настольных систем серии eXtreme Edition.

Представлен 27 июля 2006 года.

Реализованы те же технологии, что и у микропроцессора Conroe.

Варианты:

- Core 2 Extreme X6900 — 3,20 ГГц (4 Мб L2, 1066 МГц FSB) — планировался к выпуску, однако был отменен;

- Core 2 Extreme X6800 — 2,93 ГГц (4 Мб L2, 1066 МГц FSB).

Merom — 65-нм технологический процесс.

Представлен 27 июля 2006 года.

Реализованы те же технологии, что и у микропроцессора Conroe.

Варианты:

- Core 2 Duo T7700 — 2,40 ГГц (4 Мб L2, 800 МГц FSB) (платформа Santa Rosa);

- Core 2 Duo T7600 — 2,33 ГГц (4 Мб L2, 667 МГц FSB);

- Core 2 Duo T7500 — 2,20 ГГц (4 Мб L2, 800 МГц FSB);

- Core 2 Duo T7400 — 2,16 ГГц (4 Мб L2, 667 МГц FSB);

- Core 2 Duo T7300 — 2,00 ГГц (4 Мб L2, 800 МГц FSB);

- Core 2 Duo T7250 — 2,00 ГГц (2 Мб L2, 800 МГц FSB);

- Core 2 Duo T7200 — 2,00 ГГц (4 Мб L2, 667 МГц FSB);

- Core 2 Duo T7100 — 1,80 ГГц (2 Мб L2, 800 МГц FSB);

- Core 2 Duo T5800 — 2,00 ГГц (2 Мб L2, 800 МГц FSB);

- Core 2 Duo T5750 — 2,00 ГГц (2 Мб L2, 667 МГц FSB);

- Core 2 Duo T5600 — 1,83 ГГц (2 Мб L2, 667 МГц FSB);

- Core 2 Duo T5500 — 1,66 ГГц (2 Мб L2, 667 МГц FSB);

- Core 2 Duo T5200 — 1,60 ГГц (2 Мб L2, 533 МГц FSB);

- Core 2 Duo T3200 — 2,00 ГГц (1 Мб L2, 667 МГц FSB);

- Core 2 Duo L7500 — 1,60 ГГц (4 Мб L2, 800 МГц FSB) (низкое энергопотребление);

- Core 2 Duo L7400 — 1,50 ГГц (4 Мб L2, 667 МГц FSB) (низкое энергопотребление);

- Core 2 Duo L7300 — 1,40 ГГц (4 Мб L2, 800 МГц FSB) (низкое энергопотребление);

- Core 2 Duo L7200 — 1,33 ГГц (4 Мб L2, 667 МГц FSB) (низкое энергопотребление);

- Core 2 Duo U7600 — 1,20 ГГц (2 Мб L2, 533 МГц FSB) (ультрамобильный);

- Core 2 Duo U7500 — 1,06 ГГц (2 Мб L2, 533 МГц FSB) (ультрамобильный).

Kentsfield — 65-нм технологический процесс.

Микропроцессор для настольных систем с четырьмя ядрами (Quad Core).

Представлен 13 декабря 2006 года.

Количество транзисторов: 582 миллиона.

Реализованы те же технологии, что и у микропроцессора Conroe, но в отличие от него имеет 4 ядра.

Варианты:

- Core 2 Extreme QX6850 — 3,00 ГГц (2x4 Мб L2, 1333 МГц FSB) (16 июля 2007 г.);

- Core 2 Extreme QX6800 — 2,93 ГГц (2x4 Мб L2, 1066 МГц FSB) (9 апреля 2007 г.);

- Core 2 Extreme QX6700 — 2,66 ГГц (2x4 Мб L2, 1066 МГц FSB) (4 ноября 2006 г.);

- Core 2 Quad Q6700 — 2,66 ГГц (2x4 Мб L2, 1066 МГц FSB) (16 июля 2007 г.);

- Core 2 Quad Q6600 — 2,40 ГГц (2x4 Мб L2, 1066 МГц FSB) (7 января 2007 г.).

Wolfdale/Yorkfield — 45-нм технологический процесс.

Микропроцессор для настольных систем.

Поддержка инструкций SIMD: SSE4.1.

Количество транзисторов:

- 410 миллионов у моделей с двумя ядрами и 6 Мб кэш-памяти.

- 820 миллионов у моделей с четырьмя ядрами и 12 Мб кэш-памяти.

- 107 мм2 — для моделей с двумя ядрами.

- 214 мм2 — для моделей с четырьмя ядрами.

Представлены:

- 12 ноября 2007 года — 15 моделей серии Intel Xeon и модель Core 2 Extreme QX9650 (3,0Ггц);

- 7 января 2008 года — настольные и мобильные Core 2 Duo с двумя ядрами [3];

- I квартал 2008 года — настольные Core 2 Duo c четырьмя ядрами и некоторые модели Xeon.

Сокет: LGA775 (настольные), S479 (мобильные), LGA771 (Xeon).

Вместо производства транзисторов MOSFET (канальный полевой униполярный МОП-транзистор) внутри процессора на технологии с диоксидом кремния, которая работает с 1960-х годов, Intel впервые производит транзисторы по новой технологии — с диэлектриком High-K

Варианты:

- Core 2 Duo E7200 — 2,53 ГГц (3 Мб L2, 1066 МГц FSB) (11 мая 2008 года);

- Core 2 Duo E7300 — 2,66 ГГц (3 Мб L2, 1066 МГц FSB) (10 августа 2008 года);

- Core 2 Duo E7400 — 2,8 ГГц (3 Мб L2, 1066 МГц FSB) (19 октября 2008 года);

- Core 2 Duo E7500 — 2,93 ГГц (3 Мб L2, 1066 МГц FSB) (18 января 2009 года);

- Core 2 Duo E7600 — 3,06 ГГц (3 Мб L2, 1066 МГц FSB) (3 июня 2009 года);

- Core 2 Duo E8190 — 2,66 ГГц (6 Мб L2, 1333 МГц FSB) (7 января 2008 года) (аналог Е8200 но без технологии Intel VT);

- Core 2 Duo E8200 — 2,66 ГГц (6 Мб L2, 1333 МГц FSB) (7 января 2008 года);

- Core 2 Duo E8300 — 2,83 ГГц (6 Мб L2, 1333 МГц FSB) (20 апреля 2008 года);

- Core 2 Duo E8400 — 3,00 ГГц (6 Мб L2, 1333 МГц FSB) (7 января 2008 года);

- Core 2 Duo E8500 — 3,16 ГГц (6 Мб L2, 1333 МГц FSB) (7 января 2008 года);

- Core 2 Duo E8600 — 3,33 ГГц (6 Мб L2, 1333 МГц FSB) (10 августа 2008 года);

- Core 2 Quad Q8200 — 2,33 ГГц (2х2 Мб L2, 1333 МГц FSB) (31 авгу- ста 2008 года);

- Core 2 Quad Q8300 — 2,5 ГГц (2х2 Мб L2, 1333 МГц FSB) (30 нояб- ря 2008 года);

- Core 2 Quad Q8400 — 2,66 ГГц (2х2 Мб L2, 1333 МГц FSB) (19 ап- реля 2009 года);

- Core 2 Quad Q9300 — 2,50 ГГц (2x3 Мб L2, 1333 МГц FSB) (I квар- тал 2008 года);

- Core 2 Quad Q9400 — 2,66 ГГц (2x3 Мб L2, 1333 МГц FSB) (III квар- тал 2008 года);

- Core 2 Quad Q9450 — 2,66 ГГц (2x6 Мб L2, 1333 МГц FSB) (I квар- тал 2008 года);

- Core 2 Quad Q9550 — 2,83 ГГц (2x6 Мб L2, 1333 МГц FSB) (I квар- тал 2008 года);

- Core 2 Quad Q9650 — 3,00 ГГц (2x6 Мб L2, 1333 МГц FSB) (III квар- тал 2008 года);

- Core 2 Extreme QX9650 — 3,00 ГГц (2x6 Мб L2, 1333 МГц FSB) (12 ноября 2007);

- Core 2 Extreme QX9770 — 3,20 ГГц (2x6 Мб L2, 1600 МГц FSB) (I квартал 2008 года);

- Core 2 Extreme QX9775 — 3,20 ГГц (2x6 Мб L2, 1600 МГц FSB) (I квартал 2008 года) (LGA771, для Intel Skulltrail, "настольный" аналог Xeon X5482), с поддержкой симметричной многопроцессорности (SMP), ограниченной двумя микропроцессорами.

Мобильная линейка Core 2 (Penryn):

- Core 2 Duo P7350 — 2,00 ГГц (3 Мб L2, 1066 МГц FSB) (III квартал 2008 года);

- Core 2 Duo T8100 — 2,10 ГГц (3 Мб L2, 800 МГц FSB) (7 января 2008 года);

- Core 2 Duo T8300 — 2,40 ГГц (3 Мб L2, 800 МГц FSB) (7 января 2008 года);

- Core 2 Duo T9300 — 2,50 ГГц (6 Мб L2, 800 МГц FSB) (7 января 2008 года);

- Core 2 Duo T9500 — 2,60 ГГц (6 Мб L2, 800 МГц FSB) (7 января 2008 года);

- Core 2 Extreme X9000 — 2,80 ГГц (6 Мб, 800 МГц FSB) (7 января 2008 года).

Pentium Dual Core

Merom — 65-нм технологический процесс.

Представлен 27 июля 2006 года.

Реализованы те же технологии, что и у микропроцессора Conroe. Сокет: Socket 479.

Варианты:

- Intel Pentium T2310 — 1,46 ГГц (1 Мб L2, 533 МГц FSB);

- Intel Pentium T2330 — 1,60 ГГц (1 Мб L2, 533 МГц FSB);

- Intel Pentium T2370 — 1,73 ГГц (1 Мб L2, 533 МГц FSB);

- Intel Pentium T2390 — 1,86 ГГц (1 Мб L2, 533 МГц FSB).

Allendale — 65-нм технологический процесс.

Микропроцессор для настольных систем.

Представлен 21 января 2007 года.

Поддержка инструкций SIMD: SSE3.

Количество транзисторов: 167 миллионов.

Реализованы технологии:

- LaGrande Technology — аппаратная технология защиты информации;

- Execute Disable Bit;

- EIST (Enhanced Intel Speed Step Technology);

- iAMT2 (Intel Active Management Technology) — удаленное управление компьютерами;

- LGA775.

Варианты:

- Intel Pentium E2140 — 1,60 ГГц (1 Мб L2, 800 МГц FSB);

- Intel Pentium E2160 — 1,80 ГГц (1 Мб L2, 800 МГц FSB);

- Intel Pentium E2180 — 2,00 ГГц (1 Мб L2, 800 МГц FSB);

- Intel Pentium E2200 — 2,20 ГГц (1 Мб L2, 800 МГц FSB);

- Intel Pentium E2220 — 2,40 ГГц (1 Мб L2, 800 МГц FSB).

Wolfdale — 45-нм технологический процесс.

Микропроцессор для настольных систем.

Представлен 31 августа 2008 года: Pentium Dual-Core E5200.

Количество транзисторов: 228 миллионов.

Варианты:

- Intel Pentium E5200 — 2,50 ГГц (2 Мб L2, 800 МГц FSB);

- Intel Pentium E5300 — 2,60 ГГц (2 Мб L2, 800 МГц FSB) (в некоторых модификациях реализована поддержка Intel Virtualization Technology);

- Intel Pentium E5400 — 2,70 ГГц (2 Мб L2, 800 МГц FSB) (в некоторых модификациях реализована поддержка Intel Virtualization Technology).

Wolfdale-2M — 45-нм технологический процесс.

Микропроцессор для настольных систем.

Основное отличие от серии Pentium Е5000 — поддержка технологии аппаратной виртуализации Intel Virtualization Technology.

Частота системной шины (FSB): 1066 МГц.

Варианты:

- Intel Pentium E6300 — 2,80 ГГц (2 Мб L2, 1066 МГц FSB) (май 2009);

- Intel Pentium E6500 — 2,93 ГГц (2 Мб L2, 1066 МГц FSB) (август 2009).

Celeron Dual Core

Allendale — 65-нм технологический процесс.

Микропроцессор для настольных систем.

Представлен 20 января 2008 г. — версия с 512 Кб L2-кэша.

Поддержка инструкций SIMD: SSE3.

Количество транзисторов: 167 миллионов.

Реализованы технологии:

- LaGrande Technology — аппаратная технология защиты информации;

- Execute Disable Bit;

- EIST (Enhanced Intel Speed Step Technology);

- iAMT2 (Intel Active Management Technology) — удаленное управление компьютерами.

Варианты:

- Intel Celeron E1200 — 1,60 ГГц (512 Кб L2, 800 МГц FSB);

- Intel Celeron E1400 — 2,00 ГГц (512 Кб L2, 800 МГц FSB);

- Intel Celeron E1500 — 2,20 ГГц (512 Кб L2, 800 МГц FSB);

- Intel Celeron E1600 — 2,40 ГГц (512 Кб L2, 800 МГц FSB).

Wolfdale — 45-нм технологический процесс.

Микропроцессор для настольных систем.

Представлен в III квартале 2009 года.

В целом процессор аналогичен процессорам Pentium Dual Core серии E5000.

Основные особенности:

- размер кэша L2 — 1 Мб;

- поддержка технологии аппаратной виртуализации Intel Virtualization Technology.

Варианты:

- Intel Celeron E3200 — 2,40 ГГц (1 Мб L2, 800 МГц FSB);

- Intel Celeron E3300 — 2,50 ГГц (1 Мб L2, 800 МГц FSB).

Celeron (микроархитектура Core)

Conroe-L — 65-нм технологический процесс.

Представлен 27 июля 2006 года.

Количество транзисторов: 105 миллионов.

Поддержка инструкций SIMD: SSE3.

Реализованы технологии:

Варианты:

- Intel Celeron 420 — 1,60 ГГц;

- Intel Celeron 430 — 1,80 ГГц;

- Intel Celeron 440 — 2,00 ГГц;

- Intel Celeron 450 — 2,20 ГГц;

- Intel Celeron 220 — 1,2 ГГц (533 МГц FSB, TDP 19 Вт) — микропроцессор для материнских плат Mini-ITX, впаивался непосредственно в плату.

Conroe-CL — 65-нм технологический процесс.

Одноядерный микропроцессор для рабочих станций.

Варианты:

Celeron M (микроархитектура Core)

Merom-L — 65-нм технологический процесс.

Размер кэша L1: 64 Кб.

Размер кэша L2: 1 Мб.

Поддержка инструкций SIMD: SSE3.

Нет поддержки EIST (Enhanced Intel Speed Step Technology), вследствие этого не может быть частью платформы Centrino. Варианты:

Варианты:

- Intel Celeron M 520 — 1,60 ГГц;

- Intel Celeron M ULV 523 — 933 МГц (модель с низким энергопотреблением);

- Intel Celeron M 530 — 1,73 ГГц;

- Intel Celeron M 540 — 1,86 ГГц;

- Intel Celeron M 550 — 2,00 ГГц.

64-битные процессоры: EM64T — Микроархитектура Nehalem

Intel Core i5

Lynnfield — 45-нм технологический процесс.

Микропроцессор для настольных систем, позиционируется как семейство процессоров среднего уровня цены и производительности. Представлен 8 сентября 2009 года.

Представлен 8 сентября 2009 года.

Поддержка инструкций SIMD: SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2.

Реализованы технологии:

Варианты:

- Intel Core i5 750 — 2.66 ГГц (4х256 Кб L2, 8 Мб L3).

Intel Core i7

Bloomfield — 45-нм технологический процесс.

Микропроцессор для настольных систем со встроенным трехканальным контроллером DDR3-памяти.

Представлен 16 ноября 2008 года.

Поддержка инструкций SIMD: SSE3, SSSE3, SSE4.1, SSE4.2.

Количество транзисторов: 731 млн.

Реализованы технологии:

- Hyper-Threading;

- QPI;

- Intel Virtualization Technology — поддержка нескольких операционных систем на одном компьютере;

- LaGrande Technology — аппаратная технология защиты информации;

- Execute Disable Bit;

- EIST (Enhanced Intel Speed Step Technology);

- iAMT2 (Intel Active Management Technology) — удаленное управление компьютерами.

Варианты:

- Core i7 975 Extreme Edition — 3,33 ГГц (4х256 Кб L2, 8 Мб L3) — со 2 квартала 2009 года;

- Core i7 965 Extreme Edition — 3,2 ГГц (4х256 Кб L2, 8 Мб L3) — снимается с производства;

- Core i7 950 — 3,06 ГГц (4х256 Кб L2, 8 Мб L3) — со 2 квартала 2009 года;

- Core i7 940 — 2,93 ГГц (4х256 Кб L2, 8 Мб L3) — снимается с производства;

- Core i7 920 — 2,66 ГГц (4х256 Кб L2, 8 Мб L3).

Lynnfield — 45-нм технологический процесс.

Микропроцессор для настольных систем.

Представлен 8 сентября 2009 года.

Поддержка инструкций SIMD: SSE3, SSSE3, SSE4.1, SSE4.2.

Реализованы технологии:

- Hyper-Threading;

- Intel Virtualization Technology;

- Execute Disable Bit;

- EIST (Enhanced Intel Speed Step Technology).

Варианты:

- Core i7 860 — 2,80 ГГц (4х256 Кб L2, 8 Мб L3);

- Core i7 870 — 2,93 ГГц (4х256 Кб L2, 8 Мб L3).

Intel Core i7

Архитектура Nehalem была разрабатана как архитектура, которая может адаптироваться для нужд всех трех основных рынков: мобильного, настольного и серверного [73-74-75-76-77-78-79-80-81].

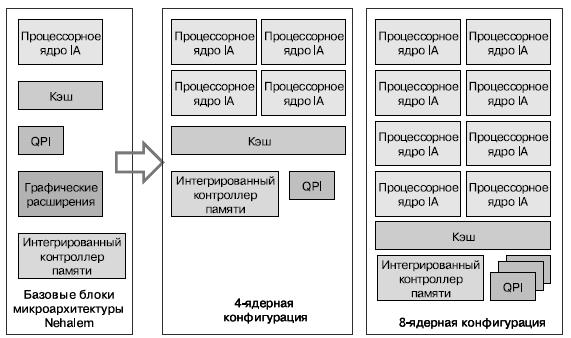

Nehalem изначально была разработана модульной — набор базовых "кирпичей", которые можно собирать, чтобы создавать разные версии архитектуры ( рис. 13.1).

Базовая архитектура следующая: четырехъядерный процессор, использующий три уровня кэш-памяти, встроенный контроллер памяти, а также высокопроизводительная система интерфейсов "точка-точка" для связи с периферией и другими процессорами в многопроцессорной конфигурации.

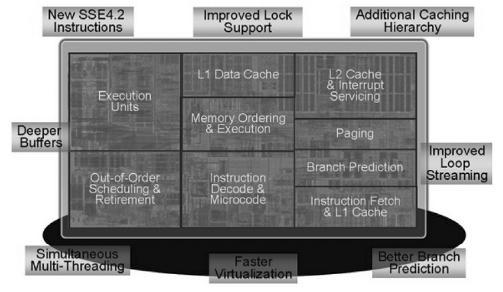

Были добавлены новые инструкции SSE. Архитектура поддерживает набор SSE 4.2.

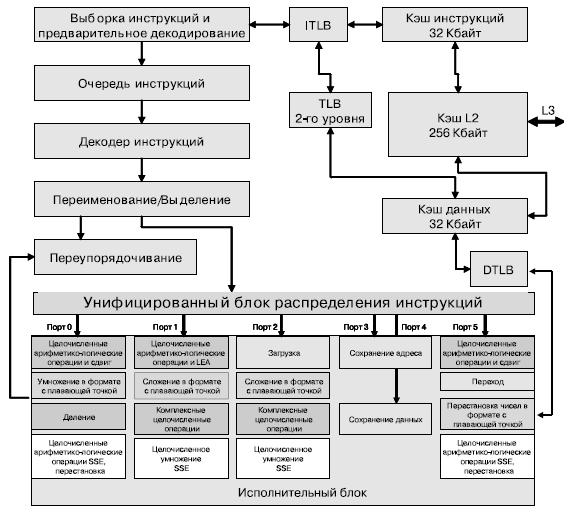

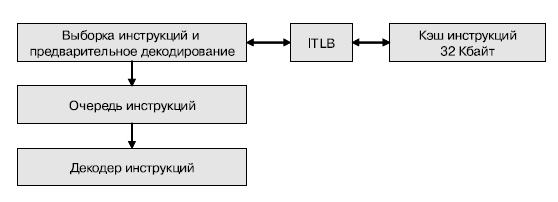

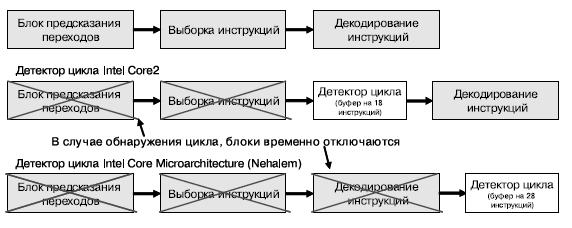

Конвейер ( рис. 13.3) — часть, которая отвечает за считывание инструкций из памяти и подготовку их для выполнения.

В конвейере Nehalem, так же как и в Conroe, присутствуют четыре блока декодирования ( рис. 13.4) — три простых и один сложный. Поддерживается функция слияния макроопераций (macro-ops fusion), обеспечивается теоретическая максимальная пропускная способность 4+1 инструкций x86 за такт.

Были оптимизированы блоки декодирования инструкций и добавлена поддержка слияния макроопераций (macro-ops fusion) для 64-битного режима. Архитектура Nehalem поддерживает большое число вариантов слияния макроопераций (что в итоге даст более частое использование этой возможности по сравнению с архитектурой Conroe).

При определении процессором цикла отключаются некоторые части конвейера. Поскольку цикл подразумевает выполнение одинаковых инструкций указанное число раз, отключается выполнение предсказания ветвлений и выборки инструкции из кэша L1 при каждой итерации цикла.

Детектор цикла Loop Stream Detector работает как небольшая кэшпамять, которая "замыкает" первые ступени конвейера в подобных ситуациях. При реализации этой техники получается двоякий прирост: снижается энергопотребление, поскольку процессор не работает над бесполезными задачами, а также увеличивается производительность путем снижения нагрузки на кэш инструкций L1 ( рис. 13.5).

В архитектуре Nehalem Intel улучшила функциональность Loop Stream Detector: буфер был увеличен — 28 инструкций; буфер находится после ступени декодирования (такое расположение позволило отключать большую часть конвейера). В Conroe буфер располагался как раз за ступенью выборки инструкций (instruction fetch). В детекторе цикла Loop Stream Detector архитектуры Nehalem хранятся уже не инструкции х86-ой архитектуры, а микрооперации ядра. В данном отношении технология чем-то напоминает концепцию кэша с отслеживаниями (trace cache) у Pentium 4. В Nehalem можно найти ряд инноваций, появившихся с архитектурой NetBurst, — если Pentium 4 использовал кэш с отслеживаниями эксклюзивно, поскольку он мог рассчитывать только на один декодер в случае промаха кэша, то Nehalem задействует четыре декодера. Loop Stream Detector можно назвать только дополнительной оптимизацией для некоторых ситуаций [77].

Улучшен блок предсказания ветвлений. Эффективность алгоритмов предсказания ветвлений критична для архитектур, где используется высокий уровень параллелизма инструкций. Ветвления разрывают параллелизм, поскольку необходимо ждать результат предыдущей инструкции, прежде чем продолжить выполнение потока инструкций. Предсказание ветвлений прогнозирует, будет взята ветвь или нет, и если ветвь будет взята, то быстро вычисляет дальнейший адрес для продолжения выполнения. Для этого применяется массив ветвлений, так называемый Branch Target Buffer (BTB), который сохраняет результаты ветвлений по мере продолжения выполнения кода (взята ветвь или нет, а также целевой адрес). К массиву прилагается алгоритм определения результата следующего ветвления.

В Nehalem есть два уровня предсказаний. Первый уровень не изменился с архитектуры Conroe, но был добавлен новый уровень с медленным доступом, который позволяет хранить большую историю ветвлений. Данная конфигурация улучшает предсказание ветвлений в некоторых приложениях, которые используют массивные участки кода, таких как базы данных, — следствие ориентации Nehalem на серверы

Return Stack Buffer хранит адрес возврата функций, когда они вызываются. В некоторых случаях этот буфер может переполняться, что приводит к ошибочным предсказаниям. Чтобы ограничить такую возможность, AMD увеличила его размер до 24 записей, а в Intel Nehalem появилась система переименования для этого буфера.

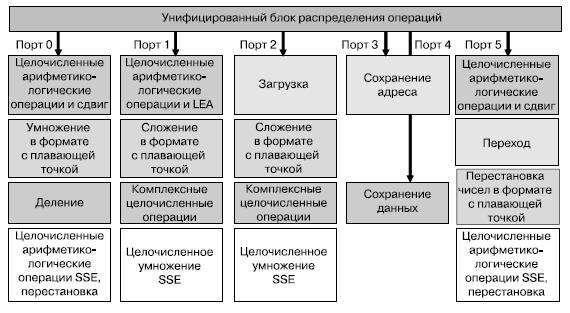

В замыкающих ступенях применяются такие же исполнительные блоки, что и в самых последних процессорах Core, но, опять же, инженеры вновь поработали над их более эффективным использованием ( рис. 13.6). Всеми исполнительными устройствами управляет единый блок распределения операций. Процессор способен выполнять до шести операций за цикл — 3 операции с памятью и 3 вычислительные.

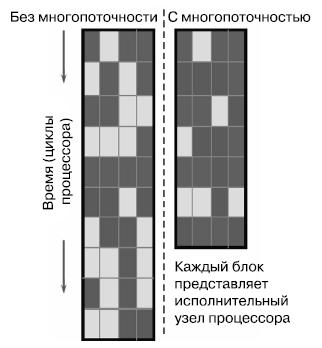

В архитертуре Nehalem реализована поддержка многопоточности (Simultaneous Multi-Threading, SMT). Поскольку физических ядер на кристалле четыре, некоторые версии Nehalem, которые используют два ядра в одной "упаковке", смогут выполнять до 16 потоков одновременно.

Многопоточность реализована по технологии Hyper-Threading. Впервые она появилась в версии Northwood архитектуры Intel NetBurst. Технология Hyper-Threading позволяет использовать параллелизм на уровне потоков, чтобы оптимизировать нагрузку исполнительных блоков ядра, в результате чего на уровне приложений одно физическое ядро превращается в два виртуальных [79].

Чтобы поддерживать параллельное выполнение потоков, некоторые ресурсы, такие как регистры, должны быть продублированы. Другие ресурсы можно совместно использовать двумя потоками, сюда входит вся логика внеочередного выполнения (буфер изменения порядка инструкций (instruction reorder buffer), исполнительные блоки и кэш). В процессоре доступно шесть исполнительных блоков, которые способны одновременно выполнять три операции работы с памятью и три операции вычисления. Если устройство выполнения не сможет обеспечить параллелизм инструкций на должном уровне, с загрузкой всех блоков, в конвейере появляются так называемые "пузырьки" — холостые такты ( рис. 13.7).

SMT пытается обеспечить параллелизм инструкций из двух потоков, а не из одного, с целью максимально уменьшить число холостых тактов. Этот подход оказывается очень эффективным, когда два потока связаны с заданиями разной природы. С другой стороны, если два потока выполняют, например, интенсивные вычисления, это лишь увеличит нагрузку на те же самые вычислительные блоки, которые будут бороться между собой за доступ к кэшу. SMT в данной ситуации может даже негативно повлиять на производительность.

В большинстве ситуаций влияние SMT на производительность — положительное, а себестоимость технологии по ресурсам невысокая, что и объясняет ее возвращение.

В случае Nehalem не все потоки создаются одинаковыми. Intel обеспечивает способ точно определить топологию процессора (число физических и логических процессоров), а программисты могут использовать механизм привязки ОС (affinity), позволяющий привязать поток к виртуальному ядру.

Буфер изменения порядка команд (reorder buffer), отслеживающий все выполняемые инструкции, был увеличен с 96 записей у Core 2 до 128 записей у Nehalem. Каждому потоку в SMT доступно 64 записи. В случае выполнения одного потока обеспечивается доступ ко всем записям, то есть потенциально устранены специфические случаи, в которых Nehalem дал бы меньшую производительность, чем предшественник.

Станция резервации (reservation station), которая отвечает за привязку инструкций к разным исполнительным блокам, тоже была увеличена с 32 до 36 записей. Но, в отличие от буфера изменения порядка команд, здесь распределение уже динамическое, поэтому поток может использовать больше или меньше записей как функцию его потребностей.

Два других буфера тоже были изменены: буфер загрузки (load buffer) и буфер хранения (store buffer). Первый получил 48 записей против 32 у Conroe, а второй — 32 вместо 20. Здесь, опять же, распределение ресурсов между потоками статическое.

Большинство новых инструкций SSE связаны с обработкой строк символов, и одно из возможных предназначений заключается в ускорении обработки XML-файлов

Две инструкции нацелены на специфические приложения; команда POPCNT, появившаяся в Barcelona, используется для подсчета числа ненулевых битов в регистре. По информации Intel, эта инструкция очень полезна в приложениях распознавания голоса и секвенирования ДНК. Последняя инструкция, CRC32, используется для ускорения расчета кода обнаружения ошибок.

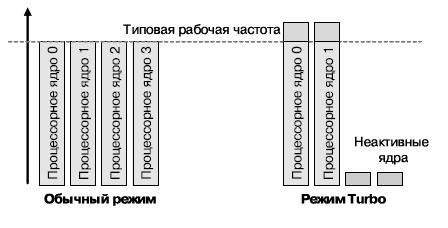

Для управления энергопотреблением применяется специализированный микроконтроллер Power Control Unit, который постоянно отслеживает температуру и энергопотребление ядер, может полностью их отключать, если ядра не используются. Благодаря этой технологии энергопотребление неиспользуемых ядер близко к нулю, в то время как до Nehalem были потери, связанные с токами утечки.

Intel реализовала довольно оригинальную технологию под названием режима Turbo. Если процессор, например, работает ниже стандартного теплового пакета, режим Turbo повышает частоту используемых ядер, вместе с тем оставаясь в пределах теплового пакета ( рис. 13.8).

Как и в случае процессора Atom, кэши L1 и L2 у Nehalem используют по восемь транзисторов на ячейку, что снижает энергопотребление за счет несколько большей площади кристалла.

Для связи ядер процессора применяется технология под названием QuickPath Interconnect (QPI), которая представляет собой встроенный контроллер памяти и очень быструю последовательную шину "точка-точка".

С технической точки зрения интерфейс QPI является двунаправленным с двумя 20-битными шинами, по одной на каждое направление, из которых 16 зарезервировано под данные, а оставшиеся четыре — под функции исправления ошибок или служебную информацию протокола. Это дает максимальную скорость 6,4 GT/s (млрд передач в секунду) или полезную пропускную способность 12,8 Гбайт/с, как на чтение, так и на передачу. Для сравнения, FSB на самых современных процессорах Intel работает с максимальной тактовой частотой 400 МГц, при этом для передачи адресов требуется два такта (200 MT/s), а данные передаются в режиме QDR, с пропускной способностью 1,6 GT/s. При 64-битной ширине FSB дает суммарную пропускную способность 12,8 Гбайт/с, но она доступна только для чтения или записи.

Поэтому интерфейс QPI дает пропускную способность до двух раз выше, если запись и чтение сбалансированы должным образом. В теоретической ситуации, когда есть только операции чтения или записи, пропускная способность будет идентична FSB. Но следует помнить, что шина FSB использовалась как для доступа к памяти, так и для передачи всех данных на периферию или между процессорами. В случае Nehalem интерфейс QPI исключительно предназначается для передачи данных на периферию, а за работу с памятью отвечает интегрированный в процессор контроллер. Связь между несколькими CPU в многосокетной конфигурации осуществляется еще одним интерфейсом QPI. Даже в самой тяжелой ситуации QPI должен показать лучшую производительность, чем FSB.

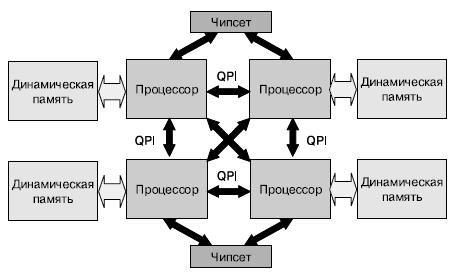

Число доступных интерфейсов QPI меняется в зависимости от ориентации на тот или иной сегмент рынка — от одного интерфейса для связи с чипсетом в односокетных конфигурациях до целых четырех для четы-рехсокетных серверов. Это позволяет создавать полносвязные четырех-процессорные системы, когда каждый процессор может получать доступ к любой области памяти через один хоп QPI, поскольку каждый процессор напрямую подключен к трем остальным ( рис. 13.9).

Топовая конфигурация Intel включает три контроллера памяти DDR3. Если установить память DDR3-1333, которую Nehalem тоже будет поддерживать, пропускная способность возрастет до 32 Гбайт/с в некоторых конфигурациях. Встроенный контроллер памяти существенно снижает задержки доступа к памяти. Раньше при добавлении CPU доступная пропускная способность оставалась прежней, однако теперь каждый новый дополнительный процессор увеличивает пропускную способность, поскольку каждый CPU обладает собственной памятью.

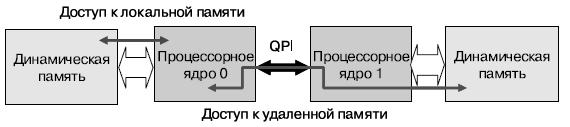

Перед нами конфигурация Non Uniform Memory Access (NUMA), то есть доступ к памяти будет обходиться по тем или иным накладным расценкам, в зависимости от того, где данные располагаются в памяти. Доступ к локальной памяти будет производиться с самыми низкими задержками и самой высокой пропускной способностью, поскольку доступ к удаленной памяти происходит через промежуточный интерфейс QPI, снижающий производительность ( рис. 13.10).

Влияние на производительность предсказать сложно, поскольку все зависит от приложения и операционной системы. Intel утверждает, что падение производительности при удаленном доступе по задержкам составляет около 70%, а пропускная способность снижается в два раза по сравнению с локальным доступом. По информации Intel, даже при удаленном доступе через интерфейс QPI задержки будут ниже, чем на предыдущих поколениях процессоров, где контроллер находился на северном мосту. Однако это касается только серверных приложений, которые уже довольно долгое время разрабатываются с учетом конфигураций NUMA.

В Nehalem каждое ядро имеет собственный кэш L2. Поскольку он выделен на каждое ядро и относительно мал (256 Кбайт), получилось обеспечить кэш очень высокой производительностью; в частности, задержки существенно улучшились по сравнению с Penryn — с 15 тактов до примерно 10 тактов.

Присутствует кэш-память третьего уровня (8 Мбайт), отвечающая за связь между ядрами. Если ядро попытается получить доступ к данным и они отсутствуют в кэше L3, то нет необходимости искать данные в собственных кэшах других ядер — там их нет. Напротив, если данные присутствуют, четыре бита, связанные с каждой строчкой кэш-памяти (один бит на ядро), показывают, могут ли данные потенциально присутствовать (потенциально, но без гарантии) в нижнем кэше другого ядра, и если да, то в каком ( рис. 13.11).

Эта техника весьма эффективна для обеспечения когерентности персональных кэшей каждого ядра, поскольку она уменьшает потребность в обмене информацией между ядрами. Кэш третьего уровня работает на других частотах по сравнению с самим чипом. Следовательно, задержка доступа на данном уровне может меняться. Здесь она составляет около 40 тактов.

Пропускная способность кэша инструкций L1 составляет 16 байт. Задержка кэша данных достигает четырех тактов, облегчая работу на высоких тактовых частотах. Было увеличено число промахов кэша данных L1, которые архитектура может обрабатывать параллельно.

Как правило, процессоры работают не с физическими адресами памяти, а с виртуальными. Такой подход позволяет выделять программе больше памяти, чем есть в компьютере, сохраняя только необходимые на данный момент данные в физической памяти, а все остальное — на жестком диске. При каждом доступе к памяти виртуальный адрес нужно переводить в физический адрес, и для сохранения соответствия приходится использовать огромную таблицу.

Для ускорения работы с виртуальной памятью применяется принцип физической адресации с применением небольшой кэш-памяти в процессоре, хранящей соответствие для нескольких недавно запрошенных адресов. Кэш-память называется Translation Lookaside Buffer (TLB).

В Nehalem используется двухуровневый TLB: кэш TLB первого уровня, разделенный для данных и инструкций. Кэш TLB L1 для данных может хранить 64 записи для маленьких страниц (4 Хбайт) или 32 записи для больших страниц (2 / 4 Mбайт), а кэш TLB L1 для инструкций может хранить 128 записей для маленьких страниц (как и в случае Core2), а также семь для крупных. Второй уровень состоит из унифицированного кэша, который может хранить до 512 записей и работает только с маленькими страницами. Цель такого улучшения заключается в увеличении производительности приложений, которые работают с большими массивами данных.

Кэш L1 TLB для данных и TLB L2 динамически распределяются между двумя потоками. Напротив, кэш L1 TLB для инструкций статически распределяется для малых страниц, а выделенный для больших страниц полностью копируется — это вполне понятно, учитывая его малый размер (семь записей на поток).

В архитектуре Core доступ к памяти приводил к ряду ограничений по производительности. Процессор был оптимизирован для доступа к адресам памяти, выровненным по 64-байтным границам, то есть по размеру одной строчки кэша. Для невыровненных данных был не только медленный доступ, но и выполнение невыровненных инструкций считывания или записи было более накладным, чем в случае выровненных инструкций, независимо от реального выравнивания данных памяти. Инструкции приводили к генерации нескольких микроопераций на декодерах, что снижало пропускную способность с данными типами инструкций. В итоге компиляторы избегали генерировать инструкции подобного типа, подставляя вместо них последовательность инструкций, которые менее накладны.

Так, чтение из памяти, при котором происходил перехлест двух строчек кэша, замедлялось примерно на 12 тактов, по сравнению с 10 тактами для записи. Инженеры Intel оптимизировали подобный тип обращений, чтобы он выполнялся быстрее. Теперь нет падения производительности при использовании невыровненных инструкций чтения/записи в случаях, когда данные выровнены в памяти. В других случаях Intel тоже оптимизировала доступ, снизив падение производительности по сравнению с архитектурой Core.

В архитектуре Conroe Intel особенно гордилась аппаратными блоками предсказания — механизмом, который следит за характером доступа к памяти и пытается предсказать, какие данные потребуются через несколько тактов. Цель заключается в том, чтобы упреждающим образом загрузить данные в кэш, где они будут располагаться ближе к процессору, и вместе с тем максимально использовать доступную пропускную способность тогда, когда процессору она не нужна.

Данная технология дает замечательные результаты с большинством настольных приложений, но в серверной среде она часто приводила к потере производительности. Есть несколько причин подобной неэффективности. Во-первых, доступы к памяти часто сложнее предсказать в серверных приложениях. Доступ к базе данных, например, отнюдь не линейный — если в памяти запрашивается какой-либо элемент данных, то это не значит, что следующим будет соседний элемент. Это ограничивает эффективность блока предварительной выборки. Но основной проблемой была пропускная способность памяти в многосокетных конфигурациях. Как мы уже говорили раньше, она уже была "узким местом" для нескольких процессоров, но помимо этого блоки предварительной выборки приводили к дополнительной нагрузке на этом уровне. Если микропроцессор не выполняет доступ к памяти, то включались блоки предварительной выборки, пытаясь использовать пропускную способность, по их предположению, свободную. Однако блоки не могли знать, нужна ли эта пропускная способность дру гому процессору. Это означало, что блоки предварительной выборки могли "отбирать" у процессора пропускную способность, которая и так была "узким местом" в таких конфигурациях.

Краткие итоги

Базовая архитектура Nehalem: четырехъядерный процессор, три уровня кэш-памяти, встроенные контроллеры памяти DDR3, высокопроизводительный системный интерфейс QPI для связи с периферией и другими процессорами в многопроцессорной конфигурации, двухуровневый TLB.

Два уровня предсказания ветвлений, поддержка многопоточности — Hyper-Threading, адаптивная система управления энергопотреблением.

Nehalem представляет собой мощное решение как для персональных компьютеров, так и для серверных и многопроцессорных систем.

Контрольные вопросы

- Дайте характеристику основных идеи архитектуры Nehalem.

- Как реализован конвейер в процессорах Nehalem?

- Как работает блок предсказания ветвлений в процессорах Nehalem?

- Каким образом реализовано управление энергопотреблением в процессорах Nehalem?

- Как работает интерфейс QPI? Характеристики интерфейса QPI

- Как организована подсистема памяти в Nehalem?

Упражнения

- Проанализируйте эффективность передачи данных между отдельными ядрами процессоров AMD Opteron и Intel Nehalem.

- Оцените производителность подсистем памяти процессоров AMD Opteron и Intel Nehalem.

- Проследите динамику развития процессоров Intel по следующим показателям — количество транзисторов, технологический процесс, пиковая производительность, потребляемая мощность, количество аппаратно поддерживаемых потоков на одно ядро, количество ядер.

- Сравните относительные показатели производительности процессоров AMD, Intel и SPARC в разрезах: пиковая производительность/потребляемая мощность и технологический процесс/потребляемая мощность. Дайте характеристику полученным зависимостям.