|

Здравствуйте Владимир (Ефименко). Я обучаюсь по программе повышения квалификации "Наноэлектронная элементная база информатики на основе полупроводников и ферромагнетиков". У меня проблема с тестом № 2 (к лекции № 2) по этой программе. Я несколько раз пытался пройти этот тест, но больше 50 баллов набрать не удаётся, хотя я всё делаю в соответствии сматериалом лекции. В заданиях этого теста есть ошибки, которые видны невооружённым глазом. Обращаюсь к Вам как к инспектору этой программы повышения квалификации. Найдите возможность исправить ошибки в тесте № 2. Из-за остановки на этом тесте я не могу двигаться дальше, а у меня очень ограниченное время на освоение этой программы. Заранее благодарен Вам за внимание к моим проблемам и помощь. |

Лекция 5: Наноэлектронная элементная база информатики на кремниевых КМДП транзисторах

КМДП логика

Базовый элемент КМДП логики – инвертор

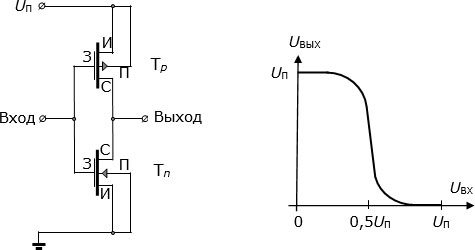

Принципиальная электрическая схема базового элемента КМДП логики показана на

рис.

5.6 слева. Она является эквивалентной схемой показанной на

рис.

5.5 структуры. Базовый элемент состоит из  -канального МДП транзистора (

-канального МДП транзистора ( ) и

) и  -канального МДП транзистора (

-канального МДП транзистора ( ). Возле символических изображений этих транзисторов обозначены их внешние выводы от истока (И), затвора (З), основы или подложки (П) и стока (С). Исток и подложка

). Возле символических изображений этих транзисторов обозначены их внешние выводы от истока (И), затвора (З), основы или подложки (П) и стока (С). Исток и подложка  -канального МДП транзистора

-канального МДП транзистора  присоединены к источнику положительного напряжения питания (

присоединены к источнику положительного напряжения питания ( ), а исток и подложка

), а исток и подложка  -канального МДП транзистора (

-канального МДП транзистора ( ) заземлены. Затворы (З) транзисторов присоединены ко входу схемы, а стоки (С) – к выходу.

) заземлены. Затворы (З) транзисторов присоединены ко входу схемы, а стоки (С) – к выходу.

Рис. 5.6. Принципиальная электрическая схема (слева) и передаточная характеристика (справа) КМДП инвертора

Справа показана передаточная характеристика схемы, т.е. зависимость напряжения на выходе инвертора ( ) от напряжения на его входе (

) от напряжения на его входе ( ). Когда напряжение на входе низкое,

). Когда напряжение на входе низкое,  -канальный транзистор (

-канальный транзистор ( ) открыт, а

) открыт, а  -канальный (

-канальный ( ) закрыт. В результате практически всё напряжение питания падает на закрытом транзисторе

) закрыт. В результате практически всё напряжение питания падает на закрытом транзисторе  , напряжение на выходе высокое и близко к

, напряжение на выходе высокое и близко к  . Когда напряжение на входе высокое,

. Когда напряжение на входе высокое,  -канальный транзистор (

-канальный транзистор ( ) закрыт,

) закрыт,  -канальный (

-канальный ( ) открыт. Поэтому напряжение на выходе низкое и мало отличается от потенциала земли.

В обоих статических состояниях электрический ток сквозь инвертор пренебрежимо мал (поскольку один из транзисторов закрыт). Существенный электрический ток протекает сквозь инвертор только при напряжении на входе, близком к

) открыт. Поэтому напряжение на выходе низкое и мало отличается от потенциала земли.

В обоих статических состояниях электрический ток сквозь инвертор пренебрежимо мал (поскольку один из транзисторов закрыт). Существенный электрический ток протекает сквозь инвертор только при напряжении на входе, близком к  . Но в логических схемах такая ситуация возможна лишь в моменты переключения из одного состояния в другое. Тогда электрический ток, протекающий сквозь транзистор, идет на перезарядку паразитных электрических емкостей.

. Но в логических схемах такая ситуация возможна лишь в моменты переключения из одного состояния в другое. Тогда электрический ток, протекающий сквозь транзистор, идет на перезарядку паразитных электрических емкостей.

КМДП логические элементы – NOR и NAND

На

рис.

5.7 показаны принципиальные электрические схемы 3-входовых КМДП логических элементов  (англ. сокращение: NOR) и

(англ. сокращение: NOR) и  (англ. сокращение: NAND). В первой схеме (слева) последовательно включены три

(англ. сокращение: NAND). В первой схеме (слева) последовательно включены три  -канальных МДП транзистора (

-канальных МДП транзистора ( ,

,  и

и  ) и параллельно включены три

) и параллельно включены три  -канальных (

-канальных ( ,

,  и

и  ). Высокий потенциал на выходе здесь устанавливается лишь тогда, когда на все 3 входа подан низкий потенциал. Лишь в этом случае все

). Высокий потенциал на выходе здесь устанавливается лишь тогда, когда на все 3 входа подан низкий потенциал. Лишь в этом случае все  -канальные транзисторы (

-канальные транзисторы ( ,

,  и

и  ) открыты, а все три

) открыты, а все три  -канальные транзисторы (

-канальные транзисторы ( ,

,  и

и  ) закрыты.

Если хотя бы на один из входов подан высокий потенциал, то соответствующий

) закрыты.

Если хотя бы на один из входов подан высокий потенциал, то соответствующий  -канальный транзистор (

-канальный транзистор ( или

или  или

или  ) закрывается, отключая выход схемы от источника питания. А соответствующий

) закрывается, отключая выход схемы от источника питания. А соответствующий  -канальный транзистор (

-канальный транзистор ( или

или  или

или  ) открывается, присоединяя выход схемы к "земле". Поэтому на выходе устанавливается низкий потенциал.

) открывается, присоединяя выход схемы к "земле". Поэтому на выходе устанавливается низкий потенциал.

В схеме, изображенной справа, три  -канальных МДП транзистора (

-канальных МДП транзистора ( ,

,  и

и  ) включены параллельно, а три

) включены параллельно, а три  -канальных МДП транзистора (

-канальных МДП транзистора ( ,

,  и

и  ) – последовательно. Поэтому на выходе низкий потенциал устанавливается лишь тогда, когда на все 3 входа подан высокий потенциал. Лишь в этом случае все

) – последовательно. Поэтому на выходе низкий потенциал устанавливается лишь тогда, когда на все 3 входа подан высокий потенциал. Лишь в этом случае все  -канальные транзисторы (

-канальные транзисторы ( ,

,  и

и  ) открыты и присоединяют выход схемы к "земле". А все

) открыты и присоединяют выход схемы к "земле". А все  -канальные транзисторы (

-канальные транзисторы ( ,

,  и

и  ) закрыты, отключая выход схемы от источника питания.

Если хотя бы на один из входов подан низкий потенциал, то соответствующий

) закрыты, отключая выход схемы от источника питания.

Если хотя бы на один из входов подан низкий потенциал, то соответствующий  -канальный транзистор (

-канальный транзистор ( ,

,  или

или  ) закрывается, отсоединяя выход схемы от "земли". А соответствующий

) закрывается, отсоединяя выход схемы от "земли". А соответствующий  -канальный транзистор (

-канальный транзистор ( ,

,  или

или  ) открывается, подключая выход схемы к источнику питания. Поэтому на выходе устанавливается высокий потенциал.

) открывается, подключая выход схемы к источнику питания. Поэтому на выходе устанавливается высокий потенциал.

Описанные логические элементы образуют функционально полный набор и позволяют строить любые логические схемы и процессоры.

Преимущества КМДП логики

Практическое отсутствие энергопотребления в статическом состоянии – это далеко не единственное положительное свойство КМДП логики. Другими ее ценными качествами являются:

- возможность работы в широком диапазоне значений напряжения питания; это, в частности, позволяет уменьшать энергопотребление, снижая напряжение питания, а также надежно функционировать даже в случае нестабилизированного напряжения питания;

- максимальный перепад потенциала при переходе от логического "0" к логической "1" (практически от потенциала "земли" до напряжения питания), что обеспечивает высокую стойкость к электромагнитным помехам;

- большое входное сопротивление независимо от состояния транзисторов (1010–1014 Ом), а, следовательно, возможность присоединять к выходу значительное количество последующих логических элементов (значительная нагрузочная способность);

- способность функционировать в широком диапазоне температур окружающей среды;

- высокое быстродействие и к тому же тем большее, чем меньшими становятся размеры транзисторов;

- малое энергопотребление при не очень высоких частотах переключения.

Основным недостатком КМДП логики является опасность пробоя статическими электрическими зарядами. Поэтому при транспортировке, хранении и во время монтажа КМДП микросхем используют усиленные меры безопасности против статических электрических зарядов. На входах и выходах КМДП интегральных схем дополнительно устанавливают защитные диодно-резистивные звенья, которые не мешают функционированию логики, но в случае необходимости создают условия для безопасного "стока" накопленных статических электрических зарядов.

Масштабирование и переход в наноразмерную область

Проектно-технологическая норма

Как вы знаете, на этапах становления и развития микроэлектронной элементной базы информатики действовал эмпирический закон Мура: количество транзисторов на полупроводниковом кристалле интегральных схем удваивалось приблизительно каждые 2 года. Это достигалось за счет повышения точности и разрешающей способности технологии и, как следствие, соответствующего уменьшения размеров транзисторов.

Минимальный размер топологических элементов интегральных схем, который гарантировано обеспечивает промышленная технология их изготовления, принято называть "проектно-технологической нормой" (ПТН) или сокращенно "проектной нормой".

От одного "поколения" интегральных схем к следующему ПТН уменьшалась приблизительно в  раз, что обеспечивало увеличение плотности интеграции транзисторов примерно вдвое. Если внимательно проанализировать структуру из двух комплементарных МДП транзисторов, показанную на

рис.

5.5, то можно увидеть, что продольный размер такой "пары" составляет не менее 12 проектно-технологических норм. Чтобы размеры пары транзисторов стали меньше 1 мкм, надо было достичь ПТН, меньше 80 нм. Поэтому можно считать, что КМДП логика стала наноэлектронной тогда, когда проектно-технологические нормы стали меньше 80 нм.

В промышленном производстве это произошло примерно в 2000-2002 гг. – на рубеже тысячелетий. И с того времени КМДП элементная база информатики стала и в самом деле наноэлектронной. Это – тот вид НЭБИ, который уже производится и используется в промышленных масштабах, работает в системах связи, в мощных серверах, в процессорах баз данных, в новейших профессиональных и персональных компьютерах и т.д.

раз, что обеспечивало увеличение плотности интеграции транзисторов примерно вдвое. Если внимательно проанализировать структуру из двух комплементарных МДП транзисторов, показанную на

рис.

5.5, то можно увидеть, что продольный размер такой "пары" составляет не менее 12 проектно-технологических норм. Чтобы размеры пары транзисторов стали меньше 1 мкм, надо было достичь ПТН, меньше 80 нм. Поэтому можно считать, что КМДП логика стала наноэлектронной тогда, когда проектно-технологические нормы стали меньше 80 нм.

В промышленном производстве это произошло примерно в 2000-2002 гг. – на рубеже тысячелетий. И с того времени КМДП элементная база информатики стала и в самом деле наноэлектронной. Это – тот вид НЭБИ, который уже производится и используется в промышленных масштабах, работает в системах связи, в мощных серверах, в процессорах баз данных, в новейших профессиональных и персональных компьютерах и т.д.

Принцип масштабирования и его качественные изменения на "наноэлектронном этапе"

На "микроэлектронном этапе" развития КМДП технологии при переходе от одной ПТН к следующей придерживались, как правило, следующего принципа масштабирования: все размеры транзисторов уменьшались пропорционально уменьшению проектно-технологической нормы. Если ПТН уменьшалась, например, в  раз, то во столько же раз уменьшались длина и ширина транзисторов, и толщина подзатворного диэлектрика. Чтобы сохранить приблизительно те же самые значения напряженности электрического поля в элементах транзисторов, приходилось приблизительно в

раз, то во столько же раз уменьшались длина и ширина транзисторов, и толщина подзатворного диэлектрика. Чтобы сохранить приблизительно те же самые значения напряженности электрического поля в элементах транзисторов, приходилось приблизительно в  раз уменьшать напряжение питания, приблизительно в

раз уменьшать напряжение питания, приблизительно в  раз повышать уровень легирования подложки.

Электрическая емкость затвора и другие паразитные емкости уменьшались при этом приблизительно в

раз повышать уровень легирования подложки.

Электрическая емкость затвора и другие паразитные емкости уменьшались при этом приблизительно в  раз. Соответственно примерно во столько же раз уменьшалось время переключения схемы и возрастала частота переключения (быстродействие) логических схем, в

раз. Соответственно примерно во столько же раз уменьшалось время переключения схемы и возрастала частота переключения (быстродействие) логических схем, в  раз уменьшались затраты энергии на переключение и возрастала плотность интеграции.

раз уменьшались затраты энергии на переключение и возрастала плотность интеграции.

На "наноэлектронном этапе" такой принцип масштабирования стало уже трудно и нецелесообразно выдерживать. Толщина подзатворного окисла приблизилась к своей границе – порядка нескольких постоянных кристаллической решетки  . Уменьшать ее дальше было рискованно из-за быстрого возрастания вероятности туннелирования электронов сквозь сверхтонкий слой диэлектрика и опасности его электрического пробоя. Был найден другой выход: вместо уменьшения толщины в качестве подзатворного диэлектрика стали использовать не

. Уменьшать ее дальше было рискованно из-за быстрого возрастания вероятности туннелирования электронов сквозь сверхтонкий слой диэлектрика и опасности его электрического пробоя. Был найден другой выход: вместо уменьшения толщины в качестве подзатворного диэлектрика стали использовать не  , а диэлектрики с более высоким значением диэлектрической постоянной.

Сначала это был преимущественно нитрид кремния и другие диэлектрики, а сейчас – оксид гафния (

, а диэлектрики с более высоким значением диэлектрической постоянной.

Сначала это был преимущественно нитрид кремния и другие диэлектрики, а сейчас – оксид гафния ( ), имеющий диэлектрическую постоянную

), имеющий диэлектрическую постоянную  (сравните со значением

(сравните со значением  в

в  ) и "удачную" для контакта с кремнием энергетическую структуру зон.

) и "удачную" для контакта с кремнием энергетическую структуру зон.

Чтобы уменьшить глубину "карманов" истока и стока, их начали создавать путем имплантации примесных ионов при относительно малом напряжении их ускорения – порядка 100-1000 В, что обеспечивает малую глубину проникновения примесных атомов в кремний. Для этого пришлось существенно изменить конструкцию установок для ионного легирования.