|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Микропроцессоры с RISC-аpхитектуpой

Микропроцессоры с RISC-аpхитектуpой

Идеология RISC-архитектуры построения процессоров (Reduced INsTRuction Set ComputINg - вычисления с сокращенным набором команд) складывалась в конце 1970-х - начале 1980-х годов, когда потребовались новые идеи для повышения производительности процессоров. Выводы различных групп исследователей были обобщены в виде так называемого правила "80/20": 80 % времени выполнения программ занимает выполнение 20 % команд, входящих в состав системы команд. То есть в определении производительности процессора основную роль играет лишь пятая часть всех команд, остальные же команды встречаются достаточно редко, и время их выполнения существенного влияния на производительность процессора не оказывает. Исходя из этого было принято решение построить процессор, в котором выделенная небольшая группа команд выполнялась бы максимально быстро за счет ее аппаратной реализации, а остальные команды либо вообще удалялись из системы команд, либо реализовывались на микропрограммном уровне.

Сложившаяся в результате этого идеология RISC-архитектуры опиралась на следующие принципы:

- набор команд сокращен до 70-100 команд (вместо нескольких сотен у CISC-микропроцессоров);

- большинство команд выполняется за 1 такт, и лишь немногие - за несколько или даже несколько десятков тактов;

- все команды обработки данных оперируют только содержимым регистров процессора, а для обращения к более медленной оперативной памяти предусмотрены исключительно инструкции вида "загрузить в регистр" и "записать в память";

- команды имеют простой, четко заданный формат;

- из набора команд исключены редко используемые инструкции, а также команд, не вписывающихся в принятый формат;

- состав системы команд должен быть удобным для применения оптимизирующих компиляторов с языков высокого уровня.

Такой подход позволил уменьшить объем аппаратуры процессора за счет сокращения блока управления примерно в 10 раз, существенно увеличить тактовую частоту работы процессора и снизить его тепловыделение.

Несмотря на свое название, основой RISC-архитектуры является то, что вся обработка сосредоточена только во внутренних регистрах микро процессора.

Так как вся обработка проходит в регистрах, отпадает необходимость в большом количестве режимов адресации операндов, а в системе команд можно применять трехадресные команды, наиболее эффективные с точки зрения организации вычислительного процесса и в то же время не имеющие их главного недостатка - большой длины команды. Простой формат команды легко поддается декодированию на соответствующей ступени работы конвейера. Вспомним, что длина команды в CISC-архитектуре IA-32 меняется в пределах от 1 до 15 байт, а наличие, формат и назначение многих полей команды неоднозначны и определяются структурой других полей.

Естественно, что этот подход потребовал использования в микропроцессоре регистровой памяти большого объема (до 128 регистров). А для обеспечения согласованной работы быстрых внутренних конвейеров и относительно медленной оперативной памяти в RISC-микропроцессорах предусматривается кэш-память большой емкости.

Наличие большого количества регистров создает хорошую основу для работы оптимизирующих компиляторов, которые позволяют эффективно использовать все конвейеры микропроцессора.

Простой формат команды и ориентация на регистровую обработку позволили безболезненно внедрить в RISC-процессорах конвейерный принцип обработки информации.

Такая организация обеспечила существенное повышение производительности RISC-микропроцессоров по сравнению с микропроцессорами CISC-архитектуры. Это привело к преобладанию МП данного типа в тех областях, где производительность являлась основополагающим фактором, например, в серверах. В то же время они не нашли своего места на наиболее развитом рынке вычислительной техники - рынке персональных компьютеров. Тому есть несколько причин:

- дороговизна RISC-процессоров и систем на их основе: изначально эти процессоры были ориентированы на мощные рабочие станции и серверы, поэтому разработчики использовали в них решения, слишком дорогие для персональных компьютеров; даже специальные, "дешевые" варианты RISC-компьютеров стоили гораздо дороже сравнимых с ними ПК на базе процессоров Intel по причине малых объемов производства;

- отсутствие широких наработок в области программного обеспечения: традиционной операционной системой для персональных компьютеров была DOS, к ней впоследствии присоединились 16разрядные версии WINdows, под которые написано огромное количество популярных и хорошо знакомых пользователям программ. Различные RISC-платформы обычно использовали несовместимые между собой разновидности Unix, для которыхсуществовало значительно меньше программ, главным образом научно-технических (для рабочих станций) либо сетевых приложений (для серверов);

- RISC-процессоры по своему основополагающему положению обладают несовместимыми с х86 наборами команд, поэтому единственным способом исполнения кода х86 была эмуляция, которая снижала производительность от десятков до сотен процентов, что сводило на нет скоростные преимущества RISC-процессоров;

- отсутствие интереса к проникновению на этот рынок у самих производителей RISC-систем: многие "серьезные" фирмы вроде DEC или Sun полагали, что нет нужды удешевлять свои RISC-станции, потому что пользователи все равно выберут их системы из-за очевидных технических преимуществ.

Развитие архитектуры RISC-микропроцессоров шло по нескольким направлениям. За счет повышения технологических возможностей производства микропроцессоров смягчились требования к составу и форматам используемых команд. В настоящее время их системы команд расширились с первоначальных 70-100 до 100-120. Увеличилось также и количество используемых форматов команд. Однако основной принцип RISC-архитектуры остается неизменным: обработка данных выполняется только над содержимым внутренних регистров МП без обращения к оперативной памяти.

Вместо требования выполнения команды за один такт используется требование получения очередного результата в очередном такте работы, то есть фактически закреплен принцип конвейерной обработки данных.

Для обработки данных микропроцессоры получили не один, а несколько конвейеров со своими исполнительными устройствами.

Наиболее известными RISC-микропроцессорами в настоящее время являются МП семейства SPARC фирмы Sun Microsystems, Alpha 21х64 фирмы Digital EquIPment и Rx000 фирмы MIPS Computer Systems. За последние годы активно внедряются в различную аппаратуру RISC-микропроцессоры семейства PowerPC. Среди фирм, выпускающих RISC-микропроцессоры, находятся также Intel, Hewlett Packard.

Совместный проект компаний Apple, Motorola и IBM - микропроцессор PowerPC (Performance Optimization With Enhanced RISC) - был ориентирован на создание недорогого, но мощного RISC-процессора и платформы для него. До появления архитектуры Intel NetBurst процессоры PowerPC почти всегда превосходили чипы Intel в скорости вычислений с плавающей точкой на десятки процентов, при этом потребляя намного меньшую мощность. По различным причинам на заключительной стадии этого проекта среди разработчиков осталась лишь компания IBM.

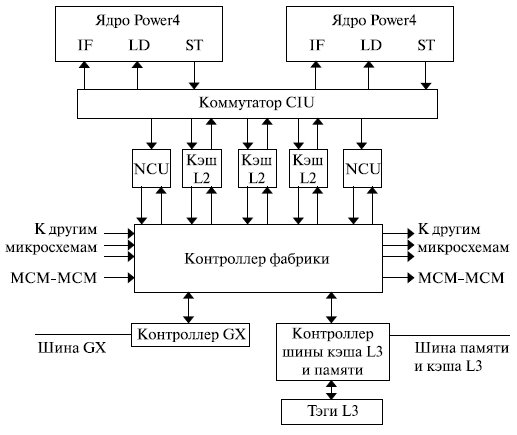

Рассмотрим организацию работы RISC-микропроцессора на примере МП Power4 фирмы IBM, который является логическим развитием архитектуры PowerPC. Микропроцессоры Power4 содержат свыше 180 млн транзисторов на кристалле и выпускаются с частотами до 1,7 ГГц при достаточно низком для высокопроизводительных процессоров уровне энергопотребления (70 Вт). С точки зрения производительности они остаются основными и практически единственными конкурентами 64-разрядных микропроцессоров архитектуры IA-64. Структура микропроцессора Power4 представлена на рис. 12.1.

Оставаясь по своей сути RISC-микропроцессором, Power4 в то же время имеет много особенностей. Отметим две главные из них.

Во-первых, Power4 стал первым микропроцессором, в котором была реализована идея размещения нескольких процессорных ядер на одной микросхеме. В состав МП Power4 входят два однотипных процессорных ядра.

Во-вторых, на кристалле Power4 содержатся интегрированные аппаратные средства, определяющие важные архитектурные черты микропро цессорных систем на его основе. В числе этих средств порты каналов, напрямую связывающих Power4 с другими процессорами внутри так называемого микросхемного модуля (Multi-Chip Module - MCM), канал ввода-вывода (шина GX), интегрированный контроллер шины оперативной памяти и кэша третьего уровня, разделяемого всеми процессорами MCM.

Каждый двухъядерный процессор Power4 упакован в керамический мультипроцессорный модуль вместе с тремя другими МП. Такой микросхемный модуль MCM, содержащий четыре МП Power4, в итоге объединяет восемь процессоров.

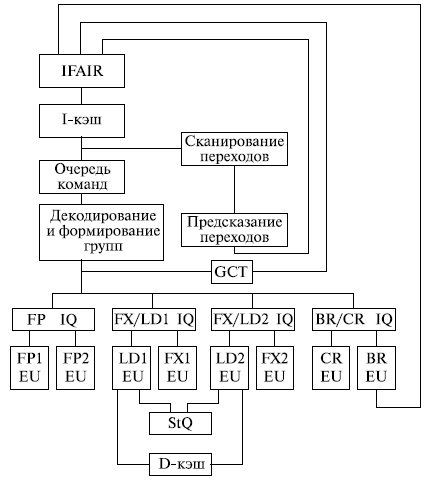

Структура ядра МП Power4 представлена на рис. 12.2.