Асинхронная ВС на принципах "data flow"

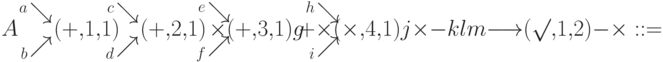

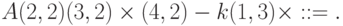

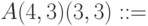

Для этого преобразуем запись на ПОЛИЗ:

Конструкции, объединенные стрелками, дают первые пять команд программы коммутации.

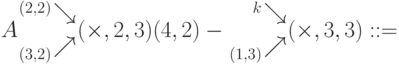

Предположим, что эти пять операций выполнены. Результаты находятся на тех же регистрах. С учетом имен этих результатов (адресов занимаемых регистров), перепишем запись на ПОЛИЗ.

Теперь условно выполняем операции следующего яруса, последовательно занимая для этого регистры буферов ПЭ:

Записываем следующие 6—9 команды программы.

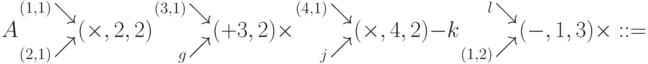

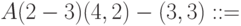

После их условного выполнения запись на ПОЛИЗ преобразуется

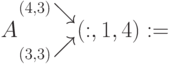

Снова назначаем ПЭ-исполнители и преобразуем эту запись:

С учетом их условного выполнения формируется запись

По ней формируем выполнение единственной операции следующего яруса

Формируем команду 12.

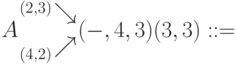

Затем вновь преобразуем запись

Формируем команду 13. Этой командой показано, что принципиально выбор ПЭ и регистра его буфера могут производиться процессором (а не программистом или транслятором); тогда по третьему адресу можно сразу указывать адрес записи в память.

Рассмотрим, как эта программа выполняется процессором коммутации (процессором).

По команде 1 в регистр (1, 1) записывается код операции "+"; в свободных регистрах ОЗП (очереди заявок к памяти) формируются инструкции ПП (процессору памяти) "считать a — послать в (1, 1), в первую позицию (в позицию первого операнда)", "считать b — послать в (1, 1), во вторую позицию".

По команде 2 формируются код операции в регистре (2, 1) и две заявки ПП на считывание и отсылку в (2, 1).

Аналогично выполняются команды 3 и 4.

По команде 5 записывается код операции "  " в

регистр (1, 2) и формируется одна заявка на считывание m и отсылку в этот регистр.

" в

регистр (1, 2) и формируется одна заявка на считывание m и отсылку в этот регистр.

По команде 6 в регистр (1, 1) записывается адрес (2, 2), первая позиция, куда должен быть отправлен результат выполнения операции. Аналогично, в регистр (2, 1) записывается адрес (2, 2), вторая позиция, как адрес отсылки результата.

Так прослеживается выполнение всех команд.

При выполнении команды 13, как уже говорилось выше, отсутствует явное задание ПЭ-исполнителя команды и адрес регистра в его буфере, где соответствующая инструкция должна формироваться. Учитывая последовательную загрузку ПЭ, здесь должен быть указан адрес (1, 4). Адрес записи результата указывается сразу, и это говорит о том, что процессор сам ведет учет и использование ПЭ.

Действительно, при программировании используется виртуальный вычислительный ресурс (иллюстрация его будет ниже), т.е. используются математические адреса процессорных элементов. Преобразование математических адресов ПЭ в физические, т.е. назначение ПЭ-исполнителей и запоминание этого назначения в таблицах производит адресный генератор. Виртуализация вычислительного ресурса обеспечивает преемственность программ при разных комплектациях, мультипрограммный и мультипроцессорный режимы, когда с одним решающим полем связаны несколько процессоров коммутации.

На рис. 10.4 представлена схема формирования и коммутации инструкций в регистрах буферов ПЭ и в очереди заявок к памяти.

Почему же в регистре буфера ПЭ предусмотрены четыре позиции для операндов?

Пятиадресные команды используются для выполнения команд коммутации типа "if - then - else".

Запрограммируем счет выражения

Cформируем три команды для коммутации счета составляющих арифметических операторов (рис. 10.5). Затем последовательно используем две команды УСЛ для коммутации внутренней и внешней конструкций типа "if - then - else".

Команда УСЛ A1 A2 A3 A4 A5 интерпретируется как A3 := if (A1) > (A2) then (A4) else (A5) и записывается в двух словах.