| Украина |

Последовательностные функциональные узлы. Триггеры

D-триггер типа "защелка"

D-триггером называют синхронный триггер, имеющий два входа - вход данных D и вход синхронизации С.

На рис. 7.4,а представлена функциональная схема D -триггера. При  изменения на входе

изменения на входе  никак не влияют на схему: триггер заперт по С -входу и находится в режиме хранения ранее записанной информации. При этом на выходах первого и второго логического элемента И-НЕ будет логическая 1, поэтому состояние третьего и четвертого логического элемента И-НЕ и, соответственно, состояние выходов

никак не влияют на схему: триггер заперт по С -входу и находится в режиме хранения ранее записанной информации. При этом на выходах первого и второго логического элемента И-НЕ будет логическая 1, поэтому состояние третьего и четвертого логического элемента И-НЕ и, соответственно, состояние выходов  и

и  не изменится и будет сохраняться ранее записанная информация, так как

не изменится и будет сохраняться ранее записанная информация, так как  и

и  перезаписывают сами себя по обратным связям. Таблица истинности приведена в табл. 7.4.

перезаписывают сами себя по обратным связям. Таблица истинности приведена в табл. 7.4.

| Управляющие сигналы | Состояние выходов | Режим работы | ||

|---|---|---|---|---|

|

|

|

|

|

| 0 | 0 |  |

|

Хранение ранее записанной информации |

| 0 | 1 |  |

|

Хранение ранее записанной информации |

| 1 | 0 | 0 | 1 | Сброс триггера |

| 1 | 1 | 1 | 0 | Установка триггера |

Передний (положительный) фронт сигнала - изменение его с уровня логического нуля на уровень логической единицы (обозначается 0/1).

Задний (отрицательный) фронт сигнала - изменение его с уровня логической единицы на уровень логического нуля (обозначается 1/0).

По переднему фронту синхросигнала  состояние входа

состояние входа  определит состояние третьего и четвертого логического элемента И-НЕ, вызывая установку в соответствующее состояние выходов

определит состояние третьего и четвертого логического элемента И-НЕ, вызывая установку в соответствующее состояние выходов  и

и  . При сохранении уровня

. При сохранении уровня  защелка прозрачна и повторяет изменения информации на

защелка прозрачна и повторяет изменения информации на  -входе. Например, если

-входе. Например, если  , тогда на вход второго элемента И-НЕ поступает решающий логический 0. На выходе первого элемента И-НЕ будет 0, который переключит выход триггера, построенного на элементах 3 и 4, в состояние

, тогда на вход второго элемента И-НЕ поступает решающий логический 0. На выходе первого элемента И-НЕ будет 0, который переключит выход триггера, построенного на элементах 3 и 4, в состояние  . Таким образом, произошла установка триггера. Информация, поступившая со входа

. Таким образом, произошла установка триггера. Информация, поступившая со входа  , теперь записана в триггер. Аналогично, если

, теперь записана в триггер. Аналогично, если  , тогда на вход первого элемента И-НЕ поступает решающий логический 0. На входе третьего элемента И-НЕ будет логическая

, тогда на вход первого элемента И-НЕ поступает решающий логический 0. На входе третьего элемента И-НЕ будет логическая  , на выходе инвертора - тоже

, на выходе инвертора - тоже  . В сочетании с

. В сочетании с  на выходе второго элемента получается логический 0, который переключит инверсный выход в состояние

на выходе второго элемента получается логический 0, который переключит инверсный выход в состояние  . По обратной связи на третьем элемента оба входа переключаются в 1, поэтому состояние прямого выхода триггера будет в состоянии

. По обратной связи на третьем элемента оба входа переключаются в 1, поэтому состояние прямого выхода триггера будет в состоянии  . Таким образом, произошел сброс триггера. Информация, поступившая со входа

. Таким образом, произошел сброс триггера. Информация, поступившая со входа  , опять-таки записана в триггер.

, опять-таки записана в триггер.

По заднему фронту сигнала  защелка фиксирует (защелкивает) последнее переключение до появления переднего фронта синхросигнала

защелка фиксирует (защелкивает) последнее переключение до появления переднего фронта синхросигнала  .

.

D -триггер переключается по сигналу на  -входе в состояние, предписанное

-входе в состояние, предписанное  -входом к этому моменту времени. На рис. 7.4,в показана временная диаграмма, иллюстрирующая работу D-триггера. В некотором смысле триггер задерживает прохождение поступившего по

-входом к этому моменту времени. На рис. 7.4,в показана временная диаграмма, иллюстрирующая работу D-триггера. В некотором смысле триггер задерживает прохождение поступившего по  -входу сигнала до появления активного (единичного) уровня на синхро-входе С (интервалы времени

-входу сигнала до появления активного (единичного) уровня на синхро-входе С (интервалы времени  и

и  на рис. 7.4,в). Поэтому название " D- триггер" можно с одной стороны рассматривать как произошедшее от англ. Delay - задержка. Другое назначение D -триггера - сохранить данные (данные по англ. data ), поступившие по

на рис. 7.4,в). Поэтому название " D- триггер" можно с одной стороны рассматривать как произошедшее от англ. Delay - задержка. Другое назначение D -триггера - сохранить данные (данные по англ. data ), поступившие по  -входу.

Синхросигналы играют роль команды "записать в триггер".

-входу.

Синхросигналы играют роль команды "записать в триггер".

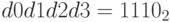

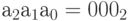

Пример включения триггера в логическую схему представлен на рис. 7.5. Здесь состояние триггеров определяется тем, какая информация поступает с мультиплексора и дешифратора. На входы схемы подаётся последовательность кодов, соответствующая ряду десятичных чисел 0, 2, 3,5, 6, 7, 1 - т.е. сначала подается  , затем

, затем  } (

} (  ,

,  ,

,  ) и т.д. На информационные линии мультиплексора постоянно подаётся код

) и т.д. На информационные линии мультиплексора постоянно подаётся код  .

.

Проанализируем работу этой схемы при подаче первого входного кода  . На выходе

. На выходе  мультиплексора будет логическая

мультиплексора будет логическая  , поскольку к нему будет передаваться информация со входа

, поскольку к нему будет передаваться информация со входа  , т.к. согласно заданию на мультиплексор подается информация

, т.к. согласно заданию на мультиплексор подается информация  . В это же время на дешифратор подается код

. В это же время на дешифратор подается код  , поэтому активен только его выход "0".

, поэтому активен только его выход "0".

Таким образом, на входы первого триггера поступают сигналы  и

и  , что приводит к переводу его выходов в состояние

, что приводит к переводу его выходов в состояние  и

и  . Таким образом, выходной сигнал схемы

. Таким образом, выходной сигнал схемы  .

.

Последний сигнал поступает в виде синхросигнала  на второй триггер, поэтому он остается в неизменном состоянии (согласно заданию это нулевое состояние

на второй триггер, поэтому он остается в неизменном состоянии (согласно заданию это нулевое состояние  и

и  ). Таким образом, выходной сигнал схемы

). Таким образом, выходной сигнал схемы  .

.

Поскольку сигналы дешифратора "5", "6" и "7" пассивны, то есть равны логическому 0, на вход второго элемента И поступает логический  , который инициирует подачу синхросигнала

, который инициирует подачу синхросигнала  на соответствующий вход третьего триггера. Он переключается в соответствии с

на соответствующий вход третьего триггера. Он переключается в соответствии с  в состояние

в состояние  и

и  . Таким образом, выходной сигнал схемы

. Таким образом, выходной сигнал схемы  .

.

Аналогично проанализировав работу схемы при подаче всех остальных кодов, получим таблицу состояний схемы (табл. 7.4).

| Входной код в десятичном выражении | Входные сигналы | Выходные сигналы | ||||

|---|---|---|---|---|---|---|

|

|

|

|

|

|

|

| 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 2 | 0 | 1 | 0 | 1 | 0 | 0 |

| 3 | 0 | 1 | 1 | 1 | 1 | 1 |

| 5 | 1 | 0 | 1 | 1 | 1 | 1 |

| 6 | 1 | 1 | 0 | 1 | 1 | 1 |

| 7 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 |

Ключевые термины

D-триггер - это синхронный триггер, имеющий два входа - вход данных  и вход синхронизации

и вход синхронизации  .

.

Задний (отрицательный) фронт сигнала - изменение его с уровня логической единицы на уровень логического нуля (обозначается 1/0).

Передний (положительный) фронт сигнала - изменение его с уровня логического нуля на уровень логической единицы (обозначается 0/1).

Последовательностное цифровое устройство -в котором выходные сигналы зависят не только от текущих значений входных сигналов, но и от последовательности значений входных сигналов, поступивших на входы в предшествующие моменты времени.

Сброс триггера - переход триггера в состояние, когда на его прямом выходе состояние логического нуля.

Триггер - это логическая схема с положительной обратной связью, которая может находиться только в одном из двух устойчивых состояний, принимаемых за состояние логического нуля и логической единицы.

Установка триггера - переход триггера в состояние, когда на его прямом выходе состояние логической единицы.

Краткие итоги

В отличие от комбинационных схем, состояние которых полностью определяется информацией, приходящей на входы, схемы триггеров обладают свойством памяти. Их состояние может зависеть от того, что подавалось на его входы в предыдущие моменты времени. Можно выделить три основных режима работы триггера: сброс, установка и хранение ранее записанной информации.

Набор для практики

Вопросы для самопроверки

- Что такое триггер?

- Нарисуйте схему RS -триггера в базисе И.

- Составьте таблицу истинности RS -триггера в базисе И.

- Нарисуйте УГО RS -триггера в базисе И.

- Нарисуйте схему RS -триггера в базисе ИЛИ.

- Составьте таблицу истинности RS -триггера в базисе ИЛИ.

- Нарисуйте УГО RS -триггера в базисе ИЛИ.

- Объясните обозначения выводов RS -триггера.

- Объясните обозначения выводов D -триггера.

- Нарисуйте временную диаграмму работы RS -триггера.

- Нарисуйте временную диаграмму работы D -триггера.