Счетные схемы ЭВМ. Счетчики и сумматоры

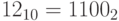

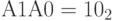

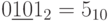

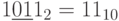

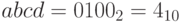

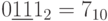

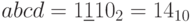

В следующем примере рассмотрим 4-входовую схему, включающую мультиплексоры и счетчики (рис. 9.9). Необходимо заполнить таблицу состояний в соответствии с заданной последовательностью входных сигналов: 2, 4, 1, 9, 10, 15, 6, 3, 13, 14.

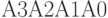

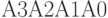

Адресные входы мультиплексора MS 1 соединены следующим образом:  - со входом " d ",

- со входом " d ",  - со входом " а ".

А адресные входы мультиплексора MS 2 соединены:

- со входом " а ".

А адресные входы мультиплексора MS 2 соединены:  - со входом " d ",

- со входом " d ",  - со входом " b ",

- со входом " b ",  - со входом " c ",

- со входом " c ",  - со входом " а ".

На информационные входы

- со входом " а ".

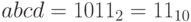

На информационные входы  MS 1 подается код

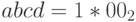

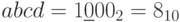

MS 1 подается код  .

Поэтому его входы

.

Поэтому его входы  и

и  соединены с источником питания + 5 В, т.е. на них постоянно подается сигнал логической

соединены с источником питания + 5 В, т.е. на них постоянно подается сигнал логической  . Входы

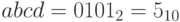

. Входы  и D 0 заземлены, т.е. на них постоянно подается сигнал логического 0. На информационные входы D 15 … D 0 мультиплексора MS 2 подается код

и D 0 заземлены, т.е. на них постоянно подается сигнал логического 0. На информационные входы D 15 … D 0 мультиплексора MS 2 подается код  . Поэтому его входы

. Поэтому его входы  ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  и

и  соединены с источником питания + 5 В, т.е. на них постоянно подается сигнал логической 1. А входы

соединены с источником питания + 5 В, т.е. на них постоянно подается сигнал логической 1. А входы  ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  и

и  заземлены, поэтому на них постоянно подается сигнал логического

заземлены, поэтому на них постоянно подается сигнал логического  .

.

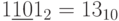

В данной схеме переключение счетчика СТ будет происходить в том случае, когда на выходе MS 1 будет логическая  , т.е. когда он будет передавать информацию со входа

, т.е. когда он будет передавать информацию со входа  или

или  . Это происходит при наличии на его адресных входах

. Это происходит при наличии на его адресных входах  кодов

кодов  и

и  . С учетом подключения

. С учетом подключения  к входной линии a, а

к входной линии a, а  - к входной линии d, получим следующее:

- к входной линии d, получим следующее:

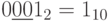

- для получения кода

на входы

на входы  нужно подать комбинацию

нужно подать комбинацию  , где "

, где "  " - любое значение (и логический

" - любое значение (и логический  , и логическая

, и логическая  ). В конкретных кодах - это 4 варианта кодов

). В конкретных кодах - это 4 варианта кодов  :

:  ;

;  ;

;  ;

;  .

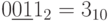

. - для получения кода

на входы abcd нужно подать комбинацию

на входы abcd нужно подать комбинацию  . В конкретных кодах - это 4 варианта кодов

. В конкретных кодах - это 4 варианта кодов  :

:  ;

;  ;

;  ;

;  .

.

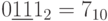

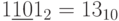

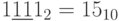

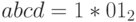

Сброс счетчика СТ будет происходить в том случае, когда на выходе MS 2 будет логическая 1, если он будет передавать информацию со входов  ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  или

или  .

.

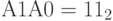

При показанном подключении входных сигналов (  - к

- к  ,

,  - к

- к  ,

,  - к

- к  ,

,  - к

- к  ) коммутация

) коммутация  к выходу MS 2 производится при подаче на

к выходу MS 2 производится при подаче на  кода

кода  . Это достигается при

. Это достигается при  .

.

Аналогично, коммутация  к выходу MS 2 производится при подаче на

к выходу MS 2 производится при подаче на  кода

кода  . Это достигается при

. Это достигается при  .

.

Аналогично, коммутация  к выходу MS 2 производится при подаче на

к выходу MS 2 производится при подаче на  кода

кода  . Это достигается при

. Это достигается при  .

.

Аналогично, коммутация  к выходу MS 2 производится при подаче на

к выходу MS 2 производится при подаче на  кода

кода  . Это достигается при

. Это достигается при  .

.

Аналогично, коммутация  к выходу MS2 производится при подаче на

к выходу MS2 производится при подаче на  кода

кода  . Это достигается при

. Это достигается при  .

.

Аналогично, коммутация  к выходу MS 2 производится при подаче на

к выходу MS 2 производится при подаче на  кода

кода  . Это достигается при

. Это достигается при  .

.

Аналогично, коммутация  к выходу MS 2 производится при подаче на

к выходу MS 2 производится при подаче на  кода

кода  . Это достигается при

. Это достигается при  .

.

Аналогично, коммутация  к выходу MS 2 производится при подаче на

к выходу MS 2 производится при подаче на  кода

кода  . Это достигается при

. Это достигается при  .

.

При остальных входных комбинациях на выход мультиплексора MS 2 подключается логический 0 с выходов  ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  .

.

), и сигнал счета (

), и сигнал счета (  ), происходит сброс счетчика. Так, в рассматриваемом примере решения такая ситуация имеет место при подаче входного кода

), происходит сброс счетчика. Так, в рассматриваемом примере решения такая ситуация имеет место при подаче входного кода  .

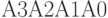

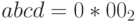

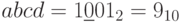

.Таблица состояний схемы приведена в табл. 9.5.

Код на входах  |

Коммутируемый вход мультиплексора MS 1 | Коммутируемый вход мультиплексора MS 2 | Состояние выводов счетчика СТ | Режим работы счетчика | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Дес. | Двоичный | Входы | Выходы | ||||||||||

|

|

|

|

|

|

|

|

|

|

||||

| 2 | 0 | 0 | 1 | 0 |  |

|

0 | 0 | 1 | 1 | 1 | 1 | Схема пассивна |

| 4 | 0 | 1 | 0 | 0 |  |

|

0 | 1 | 0 | 0 | 0 | 0 | Сброс |

| 1 | 0 | 0 | 0 | 1 |  |

|

1 | 0 | 0 | 0 | 0 | 1 | Переключение |

| 9 | 1 | 0 | 0 | 1 |  |

|

1 | 1 | 0 | 0 | 0 | 0 | Сброс |

| 10 | 1 | 0 | 1 | 0 |  |

|

0 | 0 | 0 | 0 | 0 | 0 | Схема пассивна |

| 15 | 1 | 1 | 1 | 1 |  |

|

1 | 0 | 0 | 0 | 0 | 1 | Переключение |

| 6 | 0 | 1 | 1 | 0 |  |

|

0 | 0 | 0 | 0 | 0 | 1 | Схема пассивна |

| 3 | 0 | 0 | 1 | 1 |  |

|

1 | 0 | 0 | 0 | 1 | 0 | Переключение |

| 13 | 1 | 1 | 0 | 1 |  |

|

1 | 0 | 0 | 0 | 1 | 1 | Переключение |

| 14 | 1 | 1 | 1 | 0 |  |

|

0 | 0 | 0 | 0 | 1 | 1 | Схема пассивна |

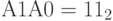

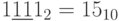

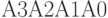

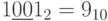

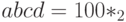

В следующем примере рассматривается 4-входовая схема (рис. 9.10), включающая дешифраторы, мультиплексоры, счетчики и сумматор. Необходимо заполнить таблицу состояний схемы в соответствии с заданной последовательностью входных сигналов: 0, 1, 2, 3, 5, 7, 10, 12, 13, 9.

Адресные входы MS соединены следующим образом:  - со входом " d ",

- со входом " d ",  - со входом " а ". На информационные входы

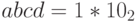

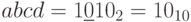

- со входом " а ". На информационные входы  мультиплексора MS подается код

мультиплексора MS подается код  . Поэтому его входы

. Поэтому его входы  ,

,  и

и  соединены с источником питания + 5 В, т.е. на них постоянно подается сигнал логической 1. А вход

соединены с источником питания + 5 В, т.е. на них постоянно подается сигнал логической 1. А вход  заземлен, т.е. на него постоянно подается сигнал логического 0. Входы DC подключены следующим образом: вход "4" соединен с входным сигналом " а ", "2" - со входом " d ", "1" - со входом " с ". У счетчика CT 1 переключающи

й вход С подключен к выходу мультиплексора MS, а вход сброса R - к выходу логического элемента ИЛИ-1. На входы элемента ИЛИ-1 согласно варианту 1 подаются сигналы с выходов "0" и "2" дешифратора DC. У счетчика CT 2 переключающий вход

заземлен, т.е. на него постоянно подается сигнал логического 0. Входы DC подключены следующим образом: вход "4" соединен с входным сигналом " а ", "2" - со входом " d ", "1" - со входом " с ". У счетчика CT 1 переключающи

й вход С подключен к выходу мультиплексора MS, а вход сброса R - к выходу логического элемента ИЛИ-1. На входы элемента ИЛИ-1 согласно варианту 1 подаются сигналы с выходов "0" и "2" дешифратора DC. У счетчика CT 2 переключающий вход  подключен к выходу логического элемента ИЛИ-2. На входы элемента ИЛИ-2 согласно варианту 1 подаются сигналы с выходов "4", "5" и "6" дешифратора DC. Вход сброса R подключен к выходу элементу И. Элемент И реализует функцию

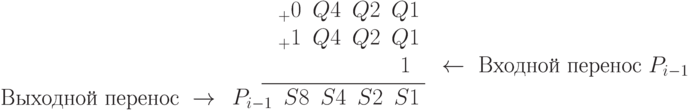

подключен к выходу логического элемента ИЛИ-2. На входы элемента ИЛИ-2 согласно варианту 1 подаются сигналы с выходов "4", "5" и "6" дешифратора DC. Вход сброса R подключен к выходу элементу И. Элемент И реализует функцию  . Входы сумматора SM подключены следующим образом. Его вход

. Входы сумматора SM подключены следующим образом. Его вход  заземлен, т. к. согласно варианту на него постоянно подается сигнал логического 0. Вход

заземлен, т. к. согласно варианту на него постоянно подается сигнал логического 0. Вход  и вход входного переноса

и вход входного переноса  соединен с источником питания + 5 В, т. к. на них постоянно подается сигнал логической

соединен с источником питания + 5 В, т. к. на них постоянно подается сигнал логической  , что отображается в табл. 9.6.

, что отображается в табл. 9.6.

С выходов "4", "2" и "1" счетчика СТ 1 сигналы  ,

,  и

и  согласно варианту поступают на входы сумматора

согласно варианту поступают на входы сумматора  ,

,  и

и  соответственно. А с выходов "4", "2" и "1" счетчика СТ 2 сигналы

соответственно. А с выходов "4", "2" и "1" счетчика СТ 2 сигналы  ,

,  и

и  поступают на входы сумматора

поступают на входы сумматора  ,

,  и

и  соответственно.

соответственно.

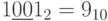

В данной схеме счетчик СТ1 переключается в том случае, когда на выходе MS будет логическая 1. Это происходит тогда, когда он будет передавать информацию со своих входов  ,

,  или

или  при наличии на его адресных входах

при наличии на его адресных входах  кодов

кодов  ,

,  или

или  соответственно. С учетом подключения

соответственно. С учетом подключения  к входной линии

к входной линии  , а

, а  - к входной линии

- к входной линии  , получим следующее:

, получим следующее:

- для получения кода

на входы

на входы  нужно подать комбинацию

нужно подать комбинацию  . В конкретных кодах - это 4 варианта кодов

. В конкретных кодах - это 4 варианта кодов  :

:  ;

;  ;

;  ;

;  ;

; - для получения кода

на входы abcd нужно подать комбинацию

на входы abcd нужно подать комбинацию  . В конкретных кодах - это 4 варианта кодов

. В конкретных кодах - это 4 варианта кодов  :

:  ;

;  ;

;  ;

;  ;

; - для получения кода

на входы

на входы  нужно подать комбинацию

нужно подать комбинацию  . В конкретных кодах - это 4 варианта кодов

. В конкретных кодах - это 4 варианта кодов  :

:  ;

;  ;

;  ;

;  .

.

Сброс счетчика СТ1 будет происходить в том случае, когда на выходе элемента ИЛИ-1 будет логическая 1, т.е. когда на выходах дешифратора "0" или "2" будет активный сигнал, равный логической 1. С учетом подключения входов дешифратора ("4" - к  , "2" - к

, "2" - к  , "1" - к

, "1" - к  ) это происходит в тех случаях, когда:

) это происходит в тех случаях, когда:

- на входы DC на "4", "2", "1" подается код

при

при  ,

,  и

и  . Это достигается при

. Это достигается при  , т.е. при подаче двух комбинаций входного кода -

, т.е. при подаче двух комбинаций входного кода -  или

или  ;

; - на входы DC на "4", "2", "1" подается код

при

при  ,

,  и

и  . Это достигается при

. Это достигается при  , т.е. при подаче двух комбинаций входного кода -

, т.е. при подаче двух комбинаций входного кода -  или

или  .

.

Переключение счетчика СТ2 будет происходить в том случае, когда на выходе элемента ИЛИ-2 будет логическая 1, т.е. когда на выходах дешифратора "4", "5" или "6" будет активный сигнал, равный логической 1. С учетом подключения входов дешифратора ("4" - к  , "2" - к

, "2" - к  , "1" - к

, "1" - к  ) это происходит в тех случаях, когда:

) это происходит в тех случаях, когда:

- на входы DC "4", "2", "1" подается код

при

при  ,

,  и

и  . Это достигается при

. Это достигается при  , т.е. при подаче двух комбинаций входного кода -

, т.е. при подаче двух комбинаций входного кода -  или

или  ;

; - на входы DC "4", "2", "1" подается код

при

при  ,

,  и

и  . Это достигается при

. Это достигается при  , т.е. при подаче двух комбинаций входного кода -

, т.е. при подаче двух комбинаций входного кода -  или

или  ;

; - на входы DC "4", "2", "1" подается код

при

при  ,

,  и

и  . Это достигается при

. Это достигается при  , т.е. при подаче двух комбинаций входного кода -

, т.е. при подаче двух комбинаций входного кода -  или

или  .

.

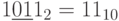

Сброс счетчика СТ2 будет происходить в том случае, когда на выходе элемента И будет логическая 1. Этот логический элемент в данной схеме реализует функцию  . Значение этой функции будет равно

. Значение этой функции будет равно  при

при  ,

,  и

и  , когда

, когда  , т.е. при подаче двух комбинаций входного кода -

, т.е. при подаче двух комбинаций входного кода -  или

или  .

.

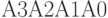

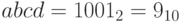

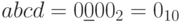

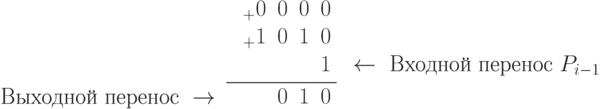

С учетом подключения сумматора SM, он осуществляет вычисления:

Например, для первой строки таблицы состояний (таблица 25) нужно произвести вычисления:

Аналогично нужно сделать вычисления для остальных строк таблицы. Все результаты приведены в табл. 9.6.

Код на входах  |

Коммутируемый вход MS | Активный выход DC | Состояние входов | Подключение входов сумматора | Состояние выходов сумматора | Режим работы схемы | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Десятичный | Двоичный | СТ 1 | СТ 2 |  |

к СТ 1 |  |

к СТ 2 |  |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

| 0 | 0 | 0 | 0 | 0 |  |

"0" | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | Сброс СТ 1 |

| 1 | 0 | 0 | 0 | 1 |  |

"2" | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | Сброс СТ 1 |

| 2 | 0 | 0 | 1 | 0 |  |

"1" | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | Пассивный |

| 3 | 0 | 0 | 1 | 1 |  |

"3" | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | Счет CT 1 |

| 5 | 0 | 1 | 0 | 1 |  |

"2" | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | Сброс СТ 1 |

| 7 | 0 | 1 | 1 | 1 |  |

"3" | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | Счет CT 1 |

| 10 | 1 | 0 | 1 | 0 |  |

"5" | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | Счет CT 1 и СТ 2 |

| 12 | 1 | 1 | 0 | 0 |  |

"4" | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | Счет CT 1 и СТ 2 |

| 13 | 1 | 1 | 0 | 1 |  |

"6" | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | Счет CT 1 и СТ 2 |

| 9 | 1 | 0 | 0 | 1 |  |

"4" | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | Счет CT 1 и СТ 2 |