|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Основные направления развития архитектуры универсальных микропроцессоров

Архитектура микропроцессора Itanium

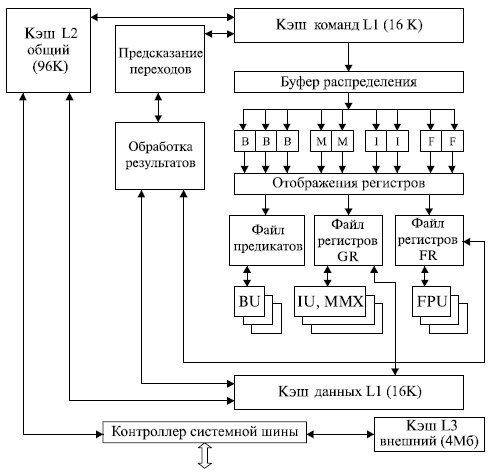

Данный микропроцессор относится к новой, 64-разрядной архитектуре IA-64. Структура микропроцессора Itanium представлена на рис. 11.2.

Системная шина Itanium позволяет соединить до 4 микропроцессоров между собой без дополнительных мостов. Ее шина данных имеет ширину 64 разряда плюс 8 разрядов для коррекции ошибок. Тактовая частота шины равна 133 МГц, но возможны 2 передачи за такт. Это обеспечивает пропускную способность 2,1 Гбайт/с. Адресная шина содержит 44 разряда.

Основные исполнительные ресурсы Itanium включают 4 целочисленных АЛУ (IU), 4 мультимедийных исполнительных устройства (MMX), 3 устройства обработки команд перехода (BU), 2 устройства с плавающей точкой, работающих с данными расширенной точности, и 2 устройства с плавающей запятой одинарной точности (FPU). Кроме того, имеются 2 устройства загрузки регистров / записи в память.

После трансляции на исполнение команды поступают в виде 128-раз рядных связок, каждая из которых содержит 3 команды и маску (рис. 11.3).

В маске указывается, какой тип исполнительных устройств требуется для той или иной команды, то есть команды компонуются таким образом, чтобы они не конфликтовали между собой из-за ресурсов микропроцессора.

Каждая команда имеет следующий формат (рис. 11.4):

В микропроцессоре имеется 9 портов четырех типов: 2 порта для команд группы М, 2 - для команд I, 2 - для команд F и 3 - для команд группы B. Они играют роль шлюзов к устройствам, выполняющим соответственно операции с памятью, целочисленные операции, операции перехода и операции с плавающей запятой. Поле маски связки команд позволяет не выдавать на одновременное выполнение больше команд, чем имеется исполнительных ресурсов микропроцессора. Команды разного типа для выполнения направляются в разные порты, и это позволяет эффективно организовать параллельное выполнение команд.

Для обеспечения более полной загрузки ресурсов Itanium в состоянии выдавать на выполнение до 6 команд за такт. При прохождении через порты осуществляется отображение виртуальных номеров регистров из программного кода в физические регистры.

Архитектура IA-64 характеризуется очень большими емкостями файлов регистров. Файл регистров общего назначения GR в IA-64 имеет емкость 128 строк. В Itanium он имеет 8 портов чтения и 6 портов записи. Эти порты позволяют поддерживать одновременно 2 М-операции и 2 I-операции за такт. Файл регистров с плавающей запятой FR имеет ту же емкость и обеспечивает одновременную работу двух М-операций и двух команд FMAC ("умножить-и-сложить"). Наконец, PRF-файл однобитных регистров-предикатов (их всего 64) имеет 15 портов чтения и 11 портов записи.

Эффективность работы функциональных устройств увеличена за счет возможности прямой подачи результата выполнения на вход другой команды, минуя запись в регистры (продвижение данных).

Целочисленное исполнительное ядро микропроцессора имеет 4 порта: 2 порта памяти и 2 собственно целочисленных порта. Все 4 порта могут выдавать на выполнение арифметические команды, команды сдвига, логические команды, команды сравнения и большинство целочисленных мультимедийных портов SIMD. М-порты могут также выполнять команды загрузки регистров / записи в память, а I-порты - более редкие целочисленные команды: проверку бит, поиск нулевого байта и некоторые виды сдвигов.

Устройства обработки чисел с плавающей точкой предполагают возможность работы с 82-разрядным представлением чисел. Это обеспечивает, в частности, форматы чисел с плавающей точкой одинарной, двойной и расширенной точности.

Глубина конвейера в МП Itanium составляет 10 стадий, что во многом определяет частоту работы микропроцессора. Она составляет от 800 МГц до 1 ГГц.

Двухпортовый кэш данных первого уровня является 4-канальным и имеет емкость 16 Кбайт с длиной строки 32 байта. В нем используется алгоритм сквозной записи. Благодаря наличию двух портов он может выполнять одновременно 2 операции загрузки регистров / записи в память в любом сочетании. Загрузка операндов с плавающей точкой всегда начинается с кэша второго уровня. Это связано с малой емкостью кэша данных первого уровня. Кэш команд первого уровня емкостью 16 Кбайт также является 4-канальным.

Двухпортовый кэш второго уровня емкостью 96 Кбайт содержит и команды, и данные. Он является 6-канальным с длиной строки 64 байта.

Как и кэш данных первого уровня, он может выполнять 2 операции с памятью за такт, но в нем используется уже алгоритм обратной записи.

Внешний кэш третьего уровня имеет емкость 4 Мбайт и длину строки 64 байта. Он является 4-канальным и может работать на частоте ядра микропроцессора.

В микроархитектуре Itanium поддерживается широкий спектр возможных размеров страниц памяти: 4/8/16/64/256 Кбайт, 1/4/16/64/256 Мбайт.

Itanium имеет очень мощную систему предсказания переходов, которая использует практически все имеющиеся в этом направлении разработки.

Во-первых, это традиционные таблицы предсказания переходов, которых в Itanium имеется два типа - BPT (Branch Prediction Table) и МBPT (Multiway Branch Prediction Table). Обе таблицы устроены, по сути, одинаково, являясь 4-канальной множественно-ассоциативной кэш-памятью на основе адресов связок. В них применяется двухуровневый предиктор с 4-разрядным полем истории (счетчики последних переходов). ВРТ имеет емкость 512 строк для обычных переходов, а МВРТ - всего 64 строки, но для переходов с ветвлением на несколько направлений. Строки МВРТ включают соответственно информацию о трех слотах переходов, а не об одном, как в ВРТ. Применение МВРТ целесообразно именно для EPICкодов с применением спекулятивной выборки и предикатов, поэтому наиболее часто употребляемыми становятся переходы со многими ветвями.

Кроме МВРТ/ВРТ для предсказания переходов используются кэш адресов перехода TAC ( Target Address Cache ), содержащий по одной строке на связку, емкостью 64 строки, регистр адресов перехода TAR ( Target Address Register ), содержащий по одной строке на пару связок, емкостью 4 строки, буфер адресов возврата RSB (RETurn Stack Buffer), используемый для команд перехода с возвратом, емкостью 8 строк. Для переходов относительно счетчика команд IP имеется два блока корректоров адреса перехода.

Содержимое TAR устанавливается командой предсказания перехода brp с суффиксом imp. Если в TAR указан соответствующий признак попадания, переход будет выполнен безотносительно к тому, что имеется в ВРТ/МВРТ. TAR содержит не только признак, но и адрес перехода. Предсказание TAR может игнорироваться только предиктором циклов (то есть когда счетчик цикла указывает, что нужно выйти из цикла).

Кэш ТАС заполняется командами перехода или аппаратурой предсказания переходов Itanium. Если в МВРТ/ВРТ имеется признак попадания, ТАС предоставляет соответствующий адрес перехода.

Таким образом, от МВРТ/ВРТ зависит, должен ли происходить переход, а адрес берется из ТАС. Если же переход отсутствует в МВРТ/ВРТ, но в ТАС есть признак попадания, переход будет осуществлен.

Если данные о переходе в ВРТ/МВРТ отсутствуют, может использоваться статическое предсказание, кодируемое в команде перехода.

Краткие итоги. В лекции рассмотрены классические направления повышения производительности микропроцессоров, показаны их ограничения. Представлены современные пути развития универсальных микропроцессоров. Подробно рассмотрены микропроцессоры Polaris, реализующие многоядерную архитектуру МП, и Itanium с архитектурой EPIC.