Состояние отечественных разработок в области высокопроизводительных вычислений

Микросхемы сигнальных процессоров 1892ВМ5Я (MC-0226, ЦПОС-02) и 1892ВМ4Я

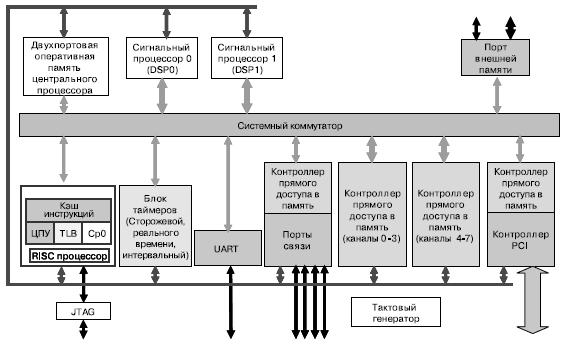

Микросхемы сигнальных процессоров 1892ВМ5Я (MC-0226, ЦПОС-02) и 1892ВМ4Я (MC-0226G, МЦОС) спроектированы по заказу НИИСИ РАН как однокристальные трехпроцессорные "системы на кристалле" (SOC) на базе IP-ядерной (IP-intellectual property) платформы "Мультикор" [87].

Все три процессорных ядра работают независимо друг от друга (каждый по своей собственной программе) и вследствие этого представляют систему на кристалле MIMD-архитектуры (MIMD — Multiple Instructions Multiple Data).

CPU-ядро является ведущим в трехпроцессорной конфигурации микросхемы и выполняет основную программу. Для CPU-ядра обеспечен доступ к ресурсам DSP-ядер, являющихся ведомыми по отношению к CPU-ядру: обмен данными CPU-ядра с ресурсами DSP-ядер выполняется по командам LOAD, STORE. Память DSP-ядер и их регистры для CPU-ядра — 32-разрядные (словные), то есть состояние двух младших разрядов адреса игнорируется.

CPU-ядро управляет работой DSP-ядер, передавая им задание (макрокоманду). Затем запускает DSP-ядра, переводя их из режима STOP в режим RUN. С другой стороны, DSP-ядра формируют следующие прерывания в CPU-ядро: программное, по переполнению стека, при выполнении команды STOP, при достижении адреса останова при исполнении программы до адреса останова или завершении требуемого числа шагов при пошаговом исполнении программы.

CPU по шине CDB имеет доступ ко всем устройствам 1892ВМ5Я. Коммутатор обеспечивает передачу данных между любым исполнительным устройством (Slave) и любым задатчиком (Master). При этом процесс передачи данных между любыми парами Slave-Master выполняется параллельно и без конфликтов.

Исполнительными устройствами являются блоки внутренней памяти (CRAM, память DSP0-DSP3) или любая внешняя память, доступная через MPORT. Задатчиками могут быть CPU, каналы DMA линковых портов, каналы DMA типа "память-память" и каналы DMA контроллера PCI.

Центральный процессор (CPU) — MIPS32-совместимый; 32-битные шины передачи адреса и данных; кэш команд объемом 16 Кбайт; оперативная память (CRAM) объемом 32 Кбайт; 5 внешних запросов прерывания, в том числе немаскируемое прерывание (NMI); устройство умножения и деления. Архитектура привилегированных ресурсов — в стиле ядра R4000 (регистры Count/Compare для прерываний реального времени; отдельный вектор обработки исключений по прерываниям). Производительность — 100 млн оп./с.

Программируемое устройство управления памятью обеспечивает:

- два режима работы — с TLB (Translation Look aside Buffer) и FM (Fixed Mapped);

- 16 строк в режиме TLB;

- JTAG IEEE 1149.1, встроенные средства отладки программ.

Два цифровых сигнальных сопроцессора (DSP0-DSP1), каждый из которых характеризуется следующими возможностями:

- "гарвардская" RISC — подобная архитектура с оригинальной системой команд и преимущественно однотактным исполнением инструкций;

- память программ PRAM объемом 16 Кбайт;

- двухпортовые памяти данных XRAM и YRAM объемом 96 и 32 Кбайт соответственно;

- 2SIMD (Single Instruction Multiple Data) организация потоков команд и данных;

- набор инструкций, совмещающий процедуры обработки и пересылки;

- Трехступенчатый конвейер по выполнению 32- и 64-разрядных инструкций.

Расширены возможности по динамическому диапазону обрабатываемых данных, позволяющие обрабатывать данные в 8/16/32-разрядных форматах с фиксированной точкой либо в одном из форматов с плавающей точкой — 24Е8 (стандарт IEEE 754) или 32Е16 (расширенный формат). Обеспечен при этом компромиссный выбор между точностью и производительностью. Имеются аппаратные меры повышения точности и динамического диапазона (блочная плавающая точка; режим насыщения; инструкции преобразования форматов)

Введена аппаратная поддержка программных циклов. Программная совместимость — снизу с сигнальным контроллером 1892ВМ2Я (МС-24).

Пиковая производительность, обеспечиваемая двумя DSP-ядрами:

- 1200 млн оп./с 32-битных операций с плавающей точкой (IEEE 754);

- 7200 млн оп./с 8-битных операций с фиксированной точкой;

- 3200 млн оп./с 16-битных операций с фиксированной точкой;

- 1600 млн оп./с 32-битных операций с фиксированной точкой.

- шина данных — 64 разряда, шина адреса — 32 разряда;

- поддержка асинхронной памяти типа SRAM, ROM, FLASH;

- поддержка синхронной памяти типа SDRAM;

- поддержка синхронной статической памяти типа SBSRAM;

- программное конфигурирование типа памяти и объема ее сегмента;

- программное задание циклов ожидания;

- формирование сигналов выборки 4 сегментов памяти;

- обеспечение обслуживания 4 внешних прерываний;

- перевод SDRAM в режим энергосбережения.

Контроллер PCI (PMSC — PCI Master-Slave controller) соответствует спецификации Local Bus Specification. Rev. 2.2; при тактовых частотах — до 100 МГц; разрядность — 32 разряда. Присутствуют режимы Master и Slave, реализовано 2 канала DMA; встроен арбитр с циклически изменяемыми приоритетами запросов.

Периферийные устройства:

- 12-канальный контроллер прямого доступа в память (DMA); 4 внешних запроса прямого доступа; специальные режимы синхронизации; поддержка двумерной и разрядно-инверсной адресации; режим передачи Flyby, подобный реализованному в ADSP-TS201: внешнее устройство — внешняя память;

- четыре линковых порта (LPORT), совместимые с ADSP21160. Имеется режим работы в качестве портов ввода-вывода общего назначения (GPIO);

- универсальный асинхронный порт (UART) типа 16550;

- набор таймеров — 32-разрядный интервальный таймер (IT), 32-разрядный таймер реального времени (RTT), 32-разрядный сторожевой таймер (WDT).

Процессор имеет узел фазовой автоподстройки частоты (PLL) c умножителем/делителем входной частоты.

Имеются режимы энергосбережения.

Все микросхемы серии совместимы по программному обеспечению снизу-вверх. К примеру, код для 1892ВМ3Т (МС-12) полностью выполняется на 1892ВМ2Я (МС-24), что обеспечивает для пользователей комфортный переход с одной микросхемы на другую.

Для программирования микросхем используются:

- инструментальная среда разработки и отладки программ MCStudio;

- инструментальная среда разработки и отладки программ MCStudio- ECL, включающая полный компилятор с языков С и С++;

- библиотеки прикладных программ;

- ядро операционной системы LINUX 2.6.19;

- операционная система реального времени QNX 6.3.

В состав отладочных комплектов для микросхем входят: отладочный модуль с установленной микросхемой серии "Мультикор", комплект кабелей и блока питания для подключения микросхемы через JTAG-порт к ПЭВМ, а также CD c документацией и инструментальным ПО — MCStudio.

Для разработчиков систем на базе микросхем серий "Мультикор" обеспечивается возможность применения новых адаптивных алгоритмов принятия решений (RLS/LNS алгоритмы), в частности, для адаптивных антенных решеток.

Микросхемы серии могут быть эффективно использованы в следующих приложениях:

- радиолокационные и гидроакустические системы;

- фазированные антенные решетки;

- связь и телекоммуникация: базовые станции, DVB-приемники и т.д.;

- сигнальная обработка: БПФ, фильтрация, корреляция, быстрая свертка;

- графические ускорители;

- мультимедийная обработка изображений и цифровое телевидение (H.264/AVC (CIF), JPEG 2000 и т. д.);

- мультимедийная обработка звука (MPEG-1 Audio Layer3 [MP3], AMR, WMA, AAC и другие звуковые кодеки);

- правление объектами с использованием высокоточных адаптивных методов;

- высокоточная обработка данных для малогабаритных мобильных и встраиваемых систем;

- системы промышленного контроля