Функционирование менеджера памяти

После знакомства со структурой виртуального адресного пространства перейдем к рассмотрению вопросов связывания виртуальных адресов с физическими адресами в рамках сегментно-страничной модели памяти Windows.

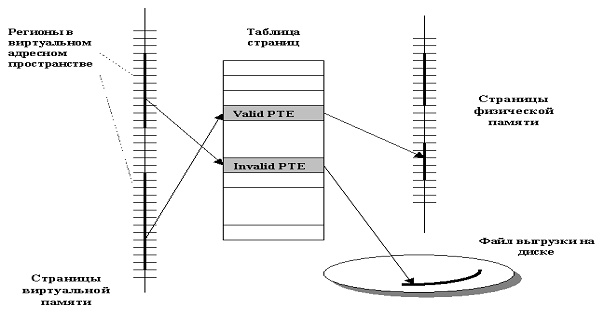

На рис. 10.1 представлено отображение различных типов виртуальных адресов в физические. Для трансляции виртуального адреса, сгенерированного процессором, нужно определить номер виртуальной страницы, содержащей данный адрес, а также принадлежность страницы к зарезервированному региону. Некоторым виртуальным страницам таблица страниц ставит в соответствие физические страницы (страничные кадры или фреймы) в оперативной памяти. Любопытно, что код режима ядра, например, драйверов, может выполнить обратную трансляцию - получение виртуального адреса по физическому. Тем страницам, которым места в физической памяти не нашлось, соответствуют теневые страницы в системном файле выгрузки. Таблица страниц здесь представлена схематично, ее более точная версия будет продемонстрирована ниже.

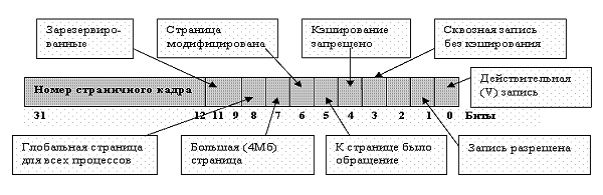

Каждая строка в таблице страниц называется PTE (page table entry). В 32-разрядных архитектурах IA-32 PTE занимает 4 байта (см. рис. 10.2).

Назначение отдельных атрибутов ясно из рисунка. Например, информация об обращении к странице или ее модификации (биты 5 и 6) позволяет собирать статистику обращений к памяти, которую используют алгоритмы выталкивания страниц. С точки зрения процесса трансляции наиболее важную роль играет бит присутствия V (Valid). Согласно терминологии, принятой в [ Руссинович ] , PTE с установленным битом V называются "действительными", а соответствующая страница находится в оперативной памяти.

При сброшенном V бите возникает страничная ошибка (page fault). Наиболее распространенный вариант page fault'а - нахождение страницы в файле выгрузки (отсутствующая страница). В этом случае первые 20 битов PTE будут указывать на смещение в страничном файле. Обработка таких ситуаций состоит в приостановке процесса, сгенерировавшего page fault, подкачке страницы с диска в свободный кадр физической памяти, модификации PTE и возобновлении неудавшейся операции. Таким образом, недействительный PTE превращается в действительный. Эта ситуация возникает часто, более того, нередки случаи обращения к одной и той же отсутствующей странице двух потоков одного процесса (конфликт ошибок страниц), которые успешно обрабатываются системой (см. [ Руссинович ] ). Помимо нужной страницы диспетчер на всякий случай загружает в память несколько, обычно от 1 до 8, соседних страниц, чтобы минимизировать количество обращений к диску (стратегия подкачки по требованию с кластеризацией).

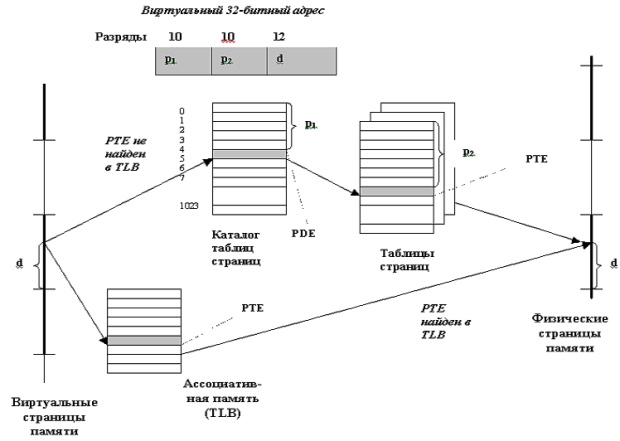

В действительности трансляция происходит более сложно (см., например, [ Карпов ] ). Существенная часть записей PTE кэшируется в ассоциативной памяти (TLB регистрах) процессора. При этом таблицу страниц в силу ее большого объема конструируют из двух уровней: каталог таблиц страниц (page directory) и таблицы страниц (page table), см. рис. 10.3.

увеличить изображение

Рис. 10.3. Трансляция адреса с использованием ассоциативной памяти и двухуровневой таблицы страниц

Размер таблицы страниц подобран таким образом, что она целиком заполняет одну страницу оперативной памяти - 4 Кб. Для быстрого нахождения таблицы страниц один из регистров процессора (CR3 в Intel) указывает на каталог таблиц страниц (page directory) данного процесса, который хранится по адресу 0хС0300000. Значение этого регистра входит в контекст процесса. Поэтому, а также потому, что при смене исполняемого потока буфер ассоциативной памяти нуждается в обновлении, несколько увеличивается время переключения контекстов. Эти особенности архитектуры хорошо известны и здесь не будут описываться подробно. В дальнейшем для упрощения в схеме трансляции адреса таблица страниц будет изображаться одномерной.

Разделяемая память

Как уже было сказано в предыдущей лекции, при отображении файла в память образуется регион в виртуальной памяти, а также сопутствующий ему объект-раздел или объект-секция (section object). Как и другие объекты, объекты-разделы управляются диспетчером объектов. В случае возникновения ошибок страниц подкачка осуществляется из страниц проецируемого файла, а не из общесистемного файла выгрузки.

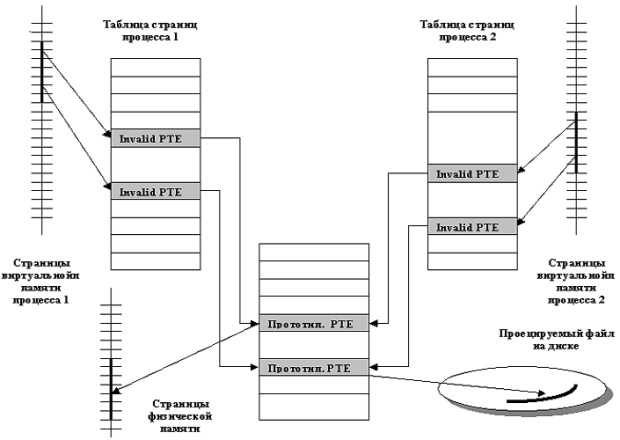

Для таких регионов формируется массив прототипных PTE, описывающих нахождение всех страниц этого фрагмента памяти. PTE таблицы страниц процесса, выполнившего отображение, ссылаются на прототипные PTE, как это показано на рис. 10.4, и тоже считаются недействительными. Если при этом другой процесс выполнил отображение этого же файла, то PTE его таблицы тоже будут ссылаться на эти же самые прототипные PTE (см. рис. 10.4). Таким образом, физические страницы памяти будут обобществлены.

увеличить изображение

Рис. 10.4. Реализация разделяемого между двумя процессами региона проецируемого в память файла

Изменения, сделанные в данном фрагменте памяти одним процессом, будут сразу же "видны" другому процессу. Таким образом, наличие таблицы прототипных PTE обеспечивает когерентность разделяемой памяти.

Более того, если третий процесс открыл тот же самый файл для обычного ввода-вывода, то уже существующее отображение будут рассматриваться в качестве буфера кэша этого файла, доступ к которому будет осуществляться через ту же самую таблицу прототипных PTE. Таким образом, все три процесса будут работать с одной и той же версией файла.

Помимо обмена информацией между различными процессами, разделяемые страницы применяются также для передачи данных между пользовательской и ядерной частями адресного пространства процесса. Примерами могут служить передача системной информации или передача информации от драйвера ввода-вывода.