|

приветствую создателей курса и благодарю за доступ к информации! понимаю, что это уже никто не исправит, но, возможно, будут следующие версии и было бы неплохо дать расшифровку сокращений имен регистров итд, дабы закрепить понимание их роли в общем процессе. |

Структура микропроцессорной системы

Структура микропроцессорной системы

МПС - сложная система, включающая в себя большое количество различных устройств. Основой ее является микропроцессор. Связь устройств ЭВМ между собой осуществляется с помощью сопряжений, которые в вычислительной технике называются интерфейсами.

Интерфейс - это совокупность программных и аппаратных средств, предназначенных для передачи информации между компонентами ЭВМ и включающих в себя электронные схемы, линии, шины и сигналы адресов, данных и управления, алгоритмы передачи сигналов и правила интерпретации сигналов устройствами.

В широком смысле интерфейс включает также механическую часть (совместимость по типоразъемам) и вспомогательные схемы, обеспечивающие электрическую совместимость устройств по уровням логических сигналов, входным и выходным токам и т. д.

Подробное изучение интерфейсов и системных шин не входит в задачи данного курса. Поэтому эти вопросы мы будем рассматривать лишь с точки зрения общего представления об организации работы микропроцессорной системы и принципах взаимодействия составляющих ее устройств.

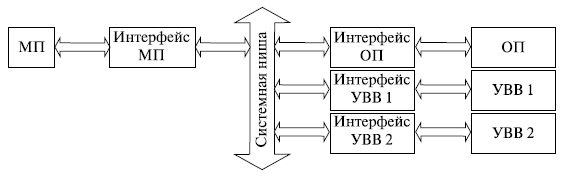

Основным способом организации МПС является магистрально-модульный (рис. 8.1): все устройства, включая и микропроцессор, представляются в виде модулей, которые соединяются между собой общей магистралью. Обмен информацией по магистрали удовлетворяет требованиям некоторого общего интерфейса, установленного для магистрали данного типа. Каждый модуль подключается к магистрали посредством специальных интерфейсных схем.

На интерфейсные схемы модулей возлагаются следующие задачи:

- обеспечение функциональной и электрической совместимости сигналов и протоколов обмена модулей и системной магистрали;

- преобразование внутреннего формата данных модуля в формат данных системной магистрали и обратно;

- обеспечение восприятия единых команд обмена информацией и преобразование их в последовательность внутренних управляющих сигналов.

Эти интерфейсные схемы могут быть достаточно сложными. Обычно они выполняются в виде специализированных микропроцессорных БИС. Такие схемы принято называть контроллерами.

Контроллеры обладают высокой степенью автономности, что позволяет обеспечить параллельную во времени работу периферийных устройств и выполнение программы обработки данных микропроцессором.

Кроме того, предварительно буферируя данные, контроллеры обеспечивают пересылку сразу для многих слов, расположенных по подряд идущим адресам, что позволяет использование так называемого "взрывного"

(burst) режима работы шины - 1 цикл адреса и следующие за ним многочисленные циклы данных.

Недостатком магистрально-модульного способа организации ЭВМ является невозможность одновременного взаимодействия более двух модулей, что ставит ограничение на производительность компьютера.

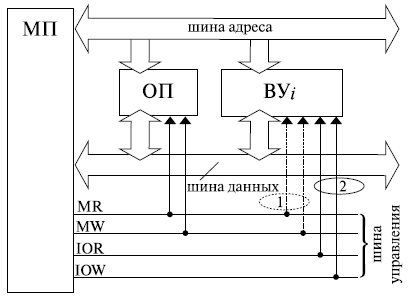

Взаимодействие микропроцессора с оперативной памятью (ОП) и внешними устройствами (ВУ) проиллюстрировано на рис. 8.2.

Микропроцессор формирует адрес внешнего устройства или ячейки оперативной памяти и вырабатывает управляющие сигналы - либо IOR/IOW при обращении на чтение/запись из внешнего устройства, либо MR/MW для чтения/записи из оперативной памяти.

Для обмена информацией с внешними устройствами в МП имеются только 2 команды:

- команда ввода IN AX, DX записывает в регистр AX число из внешнего устройства, адрес которого находится в регистре DX ; при этом вырабатывается сигнал IOR ( INput/OUTput Read ).);

- команда вывода OUT DX, AX выводит информацию из регистра AX во внешнее устройство, адрес которого находится в регистре DX ; при этом вырабатывается сигнал IOW ( INput/OUTput Write ).

Сигналы IOR/IOW формируются при выполнении только этих команд.

Формирование сигналов MR/MW происходит в командах, для которых операнд и/или приемник результата располагаются в оперативной памяти, например, ADD [EBX], AX.

В связи с этим возможны два основных способа организации адресного пространства микропроцессорной системы:

- с общим адресным пространством внешних устройств и оперативной памяти;

- с независимыми адресными пространствами.

В первом случае к портам ввода/вывода можно обращаться как к ячейкам оперативной памяти. Достоинством такого подхода является возможность использовать различные режимы адресации при обращении к внешним устройствам, а также выполнять над содержимым портов ввода/вывода различные арифметико-логические операции. Но в то же время при этом сокращается емкость адресуемой ОП и снижается защищенность системы, так как она лишается дополнительных средств защиты, связанных с выполнением команд ввода/вывода (не работает поле IOPL регистра флагов). К тому же нарушение в логике работы программы (формирование неверного адреса оперативной памяти) может привести к ложному срабатыванию внешнего устройства.

Если первый недостаток не столь существенен при современных объемах запоминающих устройств, то второй может весьма негативно сказаться на работе МПС. Возможность использования сложных режимов адресации при обращении к внешним устройствам для микропроцессорных систем на основе универсальных МП не столь важна. Поэтому в настоящее время при построении МПС предпочтение отдается второму подходу.

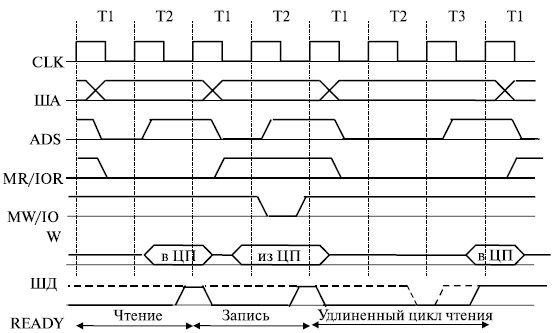

Рассмотрим особенности обмена информацией микропроцессора с внешними устройствами. Упрощенная временная диаграмма этого процесса представлена на рис. 8.3.

При таком обмене микропроцессор использует стандартный цикл шины длительностью 2 периода тактового генератора, начало которого определяется сигналом A DS шины.

Однако если в обмене задействованы относительно медленное внешнее устройство или оперативная память, которые не успевают завершить обмен в текущем цикле работы микропроцессора, то они сбрасывают сигнал READY, который проверяется микропроцессором в конце второго тактового сигнала цикла. При READY = 0 МП вставляет дополнительные такты ожидания в цикл шины, чтобы дать возможность внешнему устройству завершить операцию ввода/вывода. Однако сигнал неготовности внешнего устройства не может длиться более установленного времени (для шины ISA - 2,5 мкс), в противном случае генерируется прерывание по ошибке ввода/вывода. Это предотвращает зависание системы в случае, например, механического повреждения данного контакта.

В общем случае стандартный цикл шины при обмене уже включает несколько дополнительных тактов ожидания. При этом циклы обращения к памяти короче циклов обращения к портам ввода/вывода. Минимальная длительность цикла определяется чипсетом и может программироваться опциями BIOS Setup заданием тактов ожидания. Если ОП или внешнее устройство не нуждаются в дополнительных тактах, то их контроллеры выставляют на шину сигнал OWS, по которому дополнительные такты не вставляются.